Research progress of low-temperature Cu-Cu bonding technology for advanced packaging

-

摘要: Cu-Cu低温键合技术是先进封装的核心技术,相较于目前主流应用的Sn基软钎焊工艺,其互连节距更窄、导电导热能力更强、可靠性更优. 文中对应用于先进封装领域的Cu-Cu低温键合技术进行了综述,首先从工艺流程、连接机理、性能表征等方面较系统地总结了热压工艺、混合键合工艺实现Cu-Cu低温键合的研究进展与存在问题,进一步地阐述了新型纳米材料烧结工艺在实现低温连接、降低工艺要求方面的优越性,概述了纳米线、纳米多孔骨架、纳米颗粒初步实现可图形化的Cu-Cu低温键合基本原理. 结果表明,基于纳米材料烧结连接的基本原理,继续开发出宽工艺冗余、窄节距图形化、优良互连性能的Cu-Cu低温键合技术是未来先进封装的重要发展方向之一.Abstract: Low-temperature Cu-Cu bonding technology is the core technology for advanced packaging. Compared with the mainstream Sn-based soldering process, it can achieve finer pitch, higher electrical and thermal conductivity. In this paper, low-temperature Cu-Cu bonding technology for advanced packaging is reviewed. The research progress of low-temperature Cu-Cu bonding realized by thermal compression bonding and hybrid bonding is systematically summarized from the aspects of process flow, bonding mechanism and performance characterization. The advantages of the newly-developed nanomaterial sintering process in reducing bonding temperature and process requirements are further expounded. Mechanism of patterned nanowires, nano-porous frameworks and nanoparticles for low-temperature bonding are summarized. Low-temperature Cu-Cu bonding technology for advanced packaging are forecast.

-

Keywords:

- advanced packaging /

- hybrid bonding /

- Cu-Cu bonding /

- fine pitch /

- sintering

-

0. 序言

摩尔定律指出,集成电路上可容纳的晶体管数目及性能约每隔18 ~ 24个月便会提升一倍[1]. 随着大数据、5G、人工智能、移动互联网的迅猛发展,尤其是工艺节点到7 nm之后,物理效应、成本的限制使得依靠光刻技术驱动的摩尔定律明显放缓[2]. 在“后摩尔时代”,不再一味地追求更小的光刻工艺节点,而是依靠先进封装互连技术的创新来满足系统微型化、多功能化的需求,这将是集成电路制造行业发展的重要方向之一[3].

为了满足高性能芯片的应用需求,未来先进封装互连技术将不断向高密度、高可靠的方向发展[4]. 高密度即指焊点节距将不断减小至10 μm以下,焊点密度超过10 000个/mm2;高可靠主要指焊点在电流密度不小于106 A/cm2、服役温度不低于100 ℃等工况下服役时具有良好的稳定性能,并伴随应用领域对电子器件要求越高则上述服役参数将不断提升. 目前,主流应用的先进封装互连技术为Sn基钎料软钎焊工艺[5],主要包括回流焊和波峰焊工艺,其具有连接温度低(250 ~ 300 ℃)、成本低等优势. 对于回流焊工艺,回流过程中可发生自对中效应和塌陷效应[6],降低了对设备对中精度和基板平整度的要求. 然而,软钎焊工艺也存在诸多局限性,比如回流过程中易发生外溢效应[7],无法实现窄节距互连;其接头载流能力弱,易发生电迁移失效[8];界面反应易生成空洞和脆性相,引起机械可靠性降低等[9]. 这些瓶颈导致软钎焊工艺无法满足未来先进封装互连技术的发展要求. 近年来,Cu-Cu键合新方法发展迅速,无Sn元素的使用避免了上述问题的出现. 具体而言,Cu-Cu键合具有以下优势:① Cu在键合过程中全程保持固态,无软钎焊的外溢问题,可实现窄节距互连;② 具有优异的导电、导热性能,良好的抗电迁移能力和热机械可靠性;③ Cu是半导体制造中的常用金属,工艺兼容性好且材料成本低廉. 综合上述因素,Cu-Cu键合技术可满足高密度、高可靠互连,未来最有可能获得大规模应用. 然而,Cu-Cu键合也面临诸多新的挑战,如铜的熔点(1 083 ℃)高、自扩散速率低,难以实现低温键合. 已有研究表明,Cu-Cu直接键合需要在400 ℃的高温下才能充分发生原子扩散[10-12],如此高的温度会导致降低对中精度、损伤器件性能、增加设备要求等问题[13]. 因此,如何实现Cu-Cu低温键合已成为学术界和产业界共同关注的焦点之一.

目前,实现Cu-Cu低温键合的技术手段可分为热压键合工艺、混合键合工艺、纳米材料烧结工艺三大类. 除了需满足上述低温需求外,新工艺还要综合考虑性能(如强度、电阻)、可靠性、效率、成本、工艺兼容性等因素. 文中将对这些工艺的方法、原理进行系统归纳、总结,分析其实际应用时存在的工艺难点,并展望了Cu-Cu低温键合进一步研究的方向,以期对未来技术发展提供参考.

1. 热压键合工艺

热压键合工艺的基本原理与传统扩散焊工艺相同,即上下芯片的Cu凸点对中后直接接触,其实现原子扩散键合的主要影响参数是温度、压力、时间. 由于电镀后的Cu凸点表面粗糙并存在一定的高度差,所以键合前需要对其表面进行平坦化处理,如化学机械抛光(chemical mechanical polishing, CMP),使得键合时Cu表面能够充分接触. 基于目前研究文献,通过热压键合工艺实现Cu-Cu低温键合的方法从机理上可分为两类,即提高Cu原子扩散速率和防止/减少待键合Cu表面的氧化.

1.1 提高Cu原子扩散速率

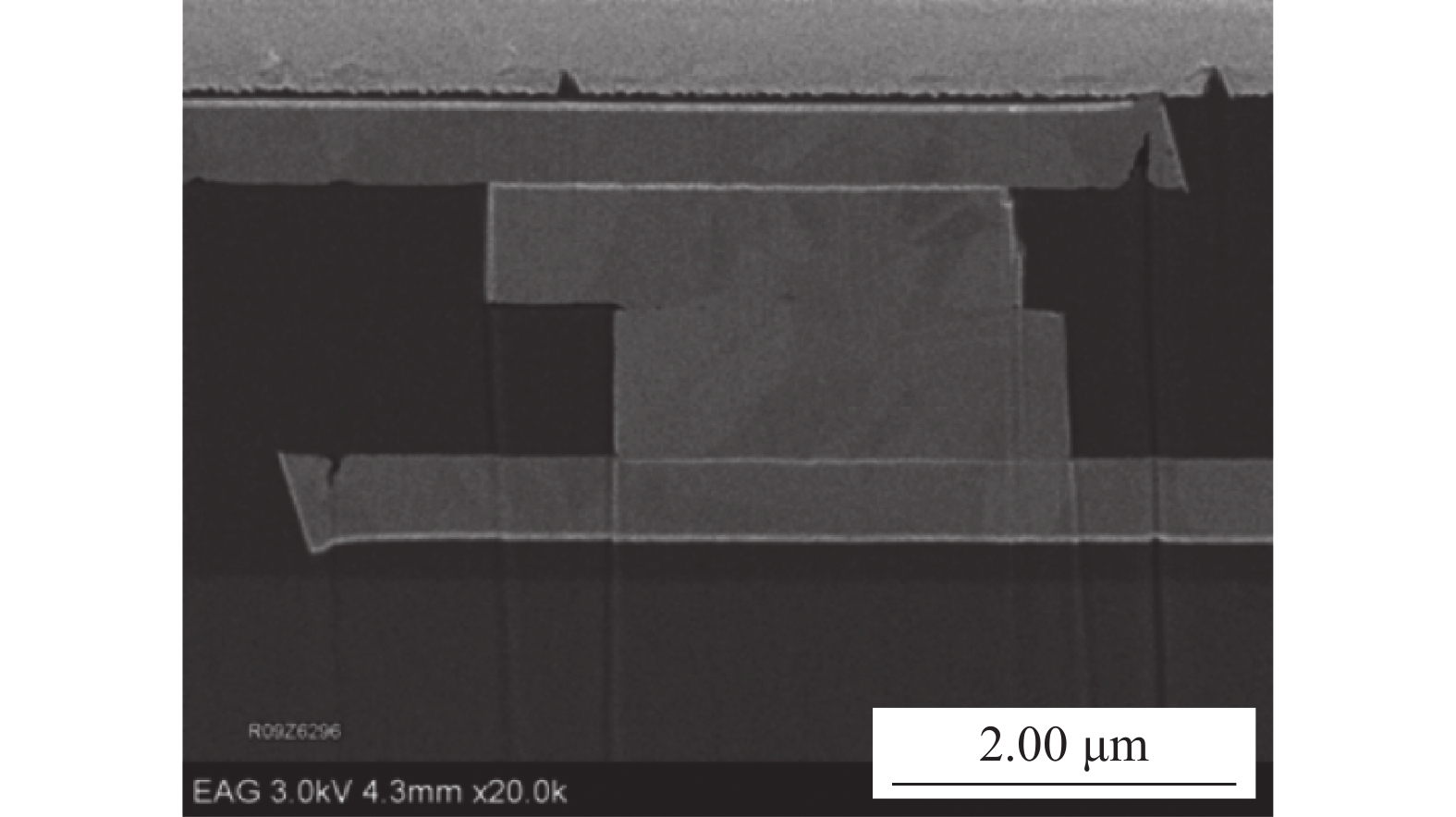

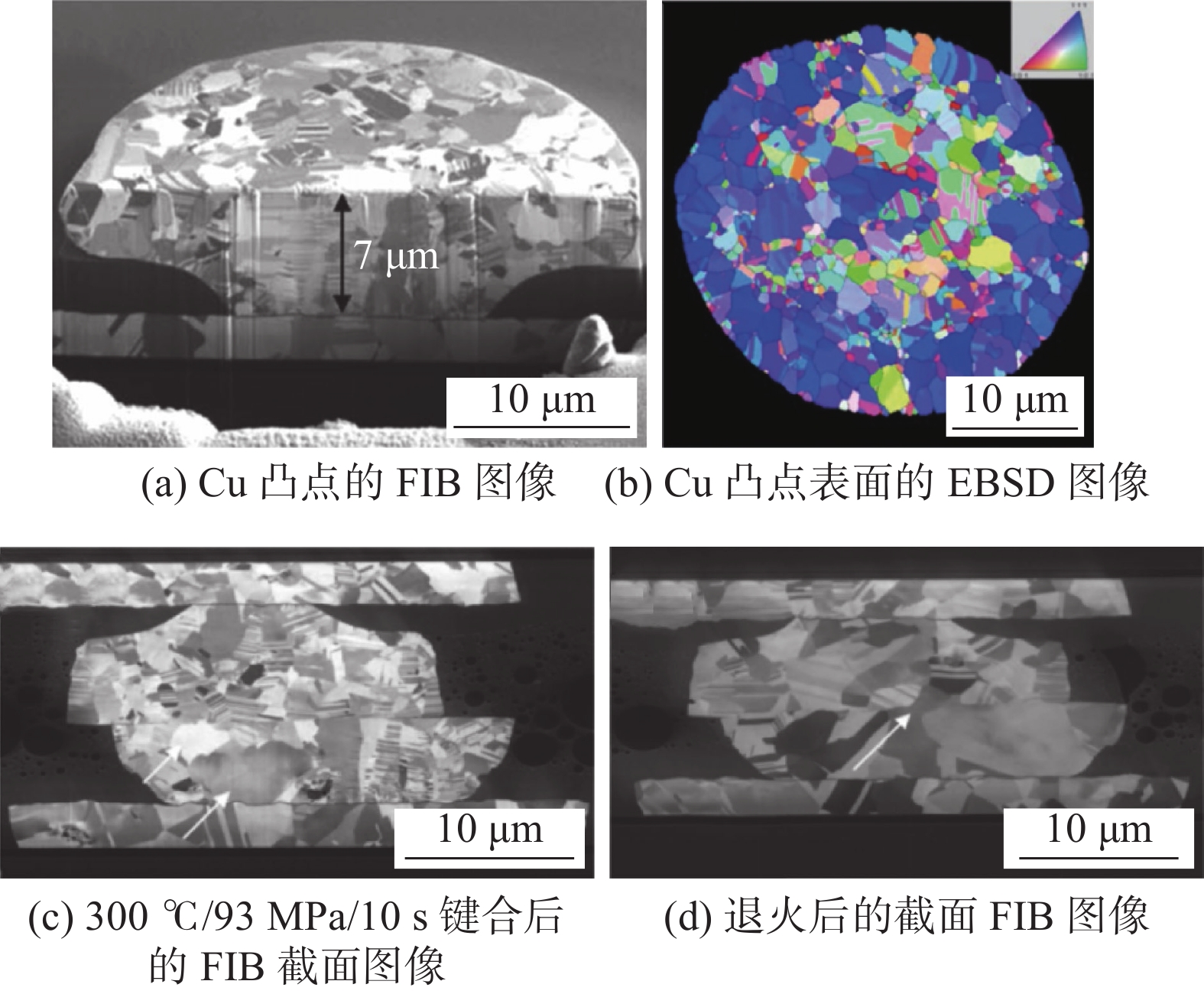

Juang[14-15],Shie[16],Ong[17],Liu[18]等人提出了电镀晶粒呈现高度(111)取向的Cu凸点用于Cu-Cu热压键合的方法,如图1所示. 已有研究表明,在150 ~ 300 ℃条件下,Cu原子在(111)晶面上的扩散速率比(100)、(110)晶面高3 ~ 6个数量级,晶粒呈现高度(111)晶向的Cu凸点可以有效提高Cu原子扩散速率,降低键合温度[18]. 利用晶粒定向生长的方法可以在300 ℃,90 MPa,10 s的条件下完成快速键合,但是键合强度和导电性能较差. 为此研究人员进一步开发出了两步键合工艺[17]:首先,电镀后的Cu凸点进行CMP并使用柠檬酸清洗去除表面氧化物,并在300 ℃,93 MPa,10 s的条件下进行预键合;然后,在300 ℃,47 MPa的真空条件下保温1 h进行退火处理,退火后的剪切强度达103 MPa,导电性能进一步改善. 图1d显示了退火后晶粒会长大至贯穿键合界面,从而可提高界面的结合强度.

![]() Figure 1. Cu-Cu bonding enabled by (111)-oriented nanotwinned Cu bumps. (a) The microbump cross-section analyzed by FIB; (b) surface orientation of an nt-Cu microbump observed by EBSD; (c) cross-sectional FIB ion-image of a Cu joint bonded at 300 ℃/93 MPa/10 s; (d) cross-sectional FIB ion-image for post-annealed sample

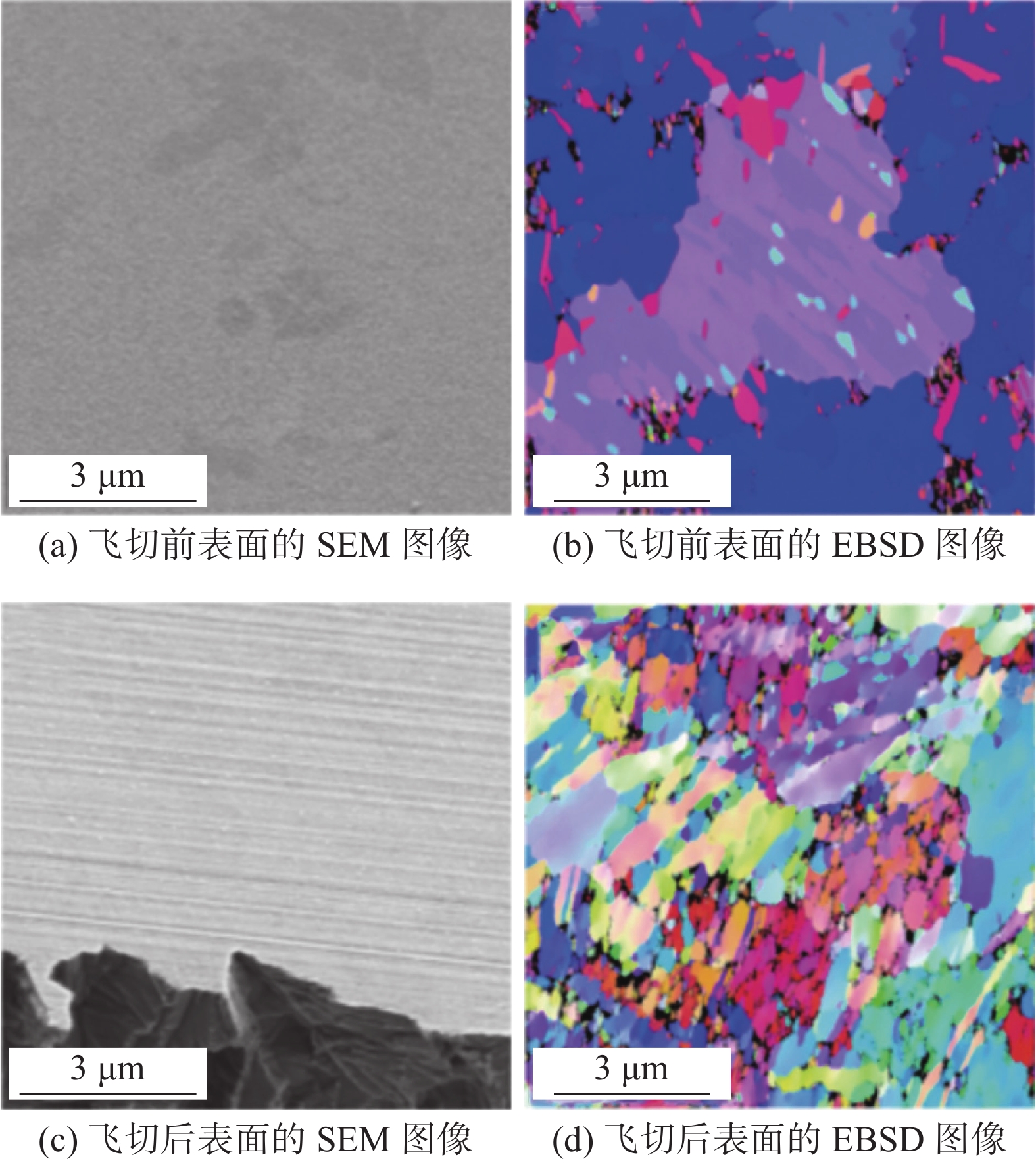

Figure 1. Cu-Cu bonding enabled by (111)-oriented nanotwinned Cu bumps. (a) The microbump cross-section analyzed by FIB; (b) surface orientation of an nt-Cu microbump observed by EBSD; (c) cross-sectional FIB ion-image of a Cu joint bonded at 300 ℃/93 MPa/10 s; (d) cross-sectional FIB ion-image for post-annealed sample此外,Sakai[19]等人采用金刚石刀头飞行切割的方法对Cu表面进行整平,如图2所示. 发现切割后的Cu表面会出现由细晶粒构成的薄层,细晶层可提高晶界扩散通量,因而降低Cu-Cu键合的温度. 最终键合在200 ℃,30 min,300 MPa的条件下完成,且界面处原子相互扩散形成了新的晶粒. 研究人员还比较了飞行切割与CMP处理后的Cu-Cu键合强度,结果表明,200 ℃连接条件下,前者的强度比后者高出近一倍. 此外,Al Farisi 等人[20]将该方法用于密封,飞行切割后的Cu密封条可在250 ℃的低温下实现键合,从而减少密封过程中的气体解吸附,降低腔体内的气压. 从图3可以看到,飞行切割后的Cu表面晶粒发生了明显细化.

![]() 图 2 飞行切割[19]Figure 2. Fly-cutting. (a) schematic illustration of fly-cutting; (b) optical images of cut Cu bumps surface

图 2 飞行切割[19]Figure 2. Fly-cutting. (a) schematic illustration of fly-cutting; (b) optical images of cut Cu bumps surface![]() 图 3 飞行切割细化表面晶粒[20]Figure 3. Fly-cutting process introduces finer grains. (a) SEM image of initial Cu surface; (b) EBSD image of initial Cu surface; (c) SEM image of cut Cu surface; (d) EBSD image of cut Cu surface

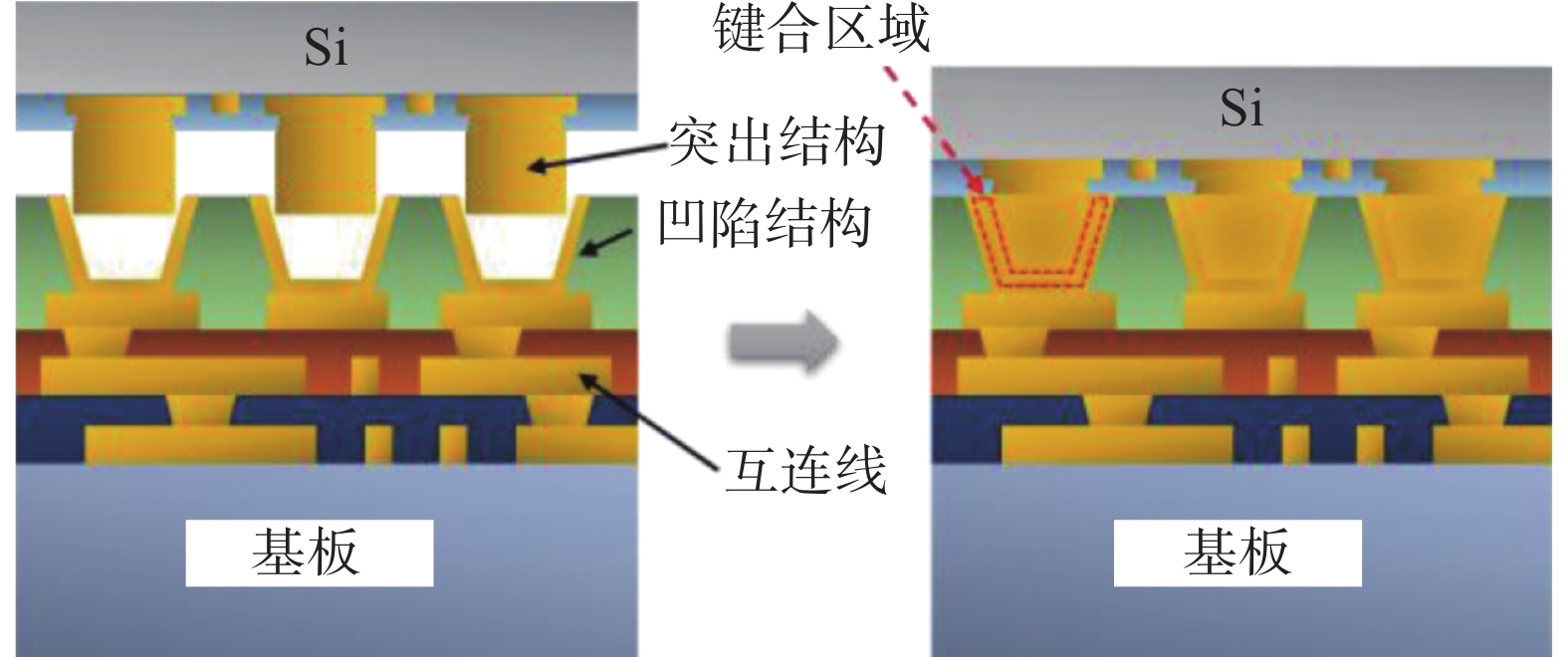

图 3 飞行切割细化表面晶粒[20]Figure 3. Fly-cutting process introduces finer grains. (a) SEM image of initial Cu surface; (b) EBSD image of initial Cu surface; (c) SEM image of cut Cu surface; (d) EBSD image of cut Cu surface进一步地,为降低对CMP/飞行切割整平工艺的依赖,Yang[21],Chou[22]等人提出了插入式Cu-Cu键合工艺,其原理如图4所示. 首先通过电镀工艺制作出异型结构的待键合Cu表面,一面直径较小的Cu为突出结构,另一面直径较大的Cu为凹陷结构,二者对中后形成插入式结构. 在加压过程中突出结构的Cu和凹陷结构的Cu发生相对滑移和应力集中,产生一定的热效应,加速原子扩散. 这种方法可以在150 ℃的条件下完成键合,键合后的界面如图5所示. 可靠性测试表明,该方法经过1 000个热循环测试(thermal cycling test,TCT,−55 ~ 125 ℃)和96 h,130 ℃,85%湿度的加速老化测试(highly accelerated stress Test,HAST)后,接头电阻无明显变化. 这种方法无需CMP工艺,对待键合表面的粗糙度有一定容忍度. 但是,为了使上下Cu结构发生较大塑性变形而充分接触,需要施加高达500 MPa以上的压力.

![]() 图 4 插入式Cu-Cu键合的原理图[22]Figure 4. Schematic of pillar-concave bonding scheme

图 4 插入式Cu-Cu键合的原理图[22]Figure 4. Schematic of pillar-concave bonding scheme![]() 图 5 键合后的SEM图像[22]Figure 5. SEM cross-sectional view of Cu-Cu bonding. (a) with bonding condition of 150 ℃, 1 min, 500 MPa; (b) bottom bonding interface; (c) sidewall bonding interface

图 5 键合后的SEM图像[22]Figure 5. SEM cross-sectional view of Cu-Cu bonding. (a) with bonding condition of 150 ℃, 1 min, 500 MPa; (b) bottom bonding interface; (c) sidewall bonding interface1.2 防止/减少待键合表面氧化

Cu在高温键合的情况下容易发生氧化,阻碍Cu原子的扩散. Takagi[23],Suga[24],Shigetou[25]等人提出了表面活化键合(Surface Activated Bonding,SAB)的方法. 该方法在超高真空条件下(10−8 torr)采用等离子体轰击待键合Cu表面,去除氧化物和其他污染物,达到原子级的表面清洁度,并在室温、无压力条件下进行预键合. 室温条件键合可以保证有更好的对中精度,报道中SAB可实现6 μm的窄节距互连. 由图6可以看到,预键合后仍存在明显界面,所以该方法往往需要250 ~ 300 ℃的高温退火. SAB表面处理和键合过程都需要在高真空条件下完成,对设备要求非常高.

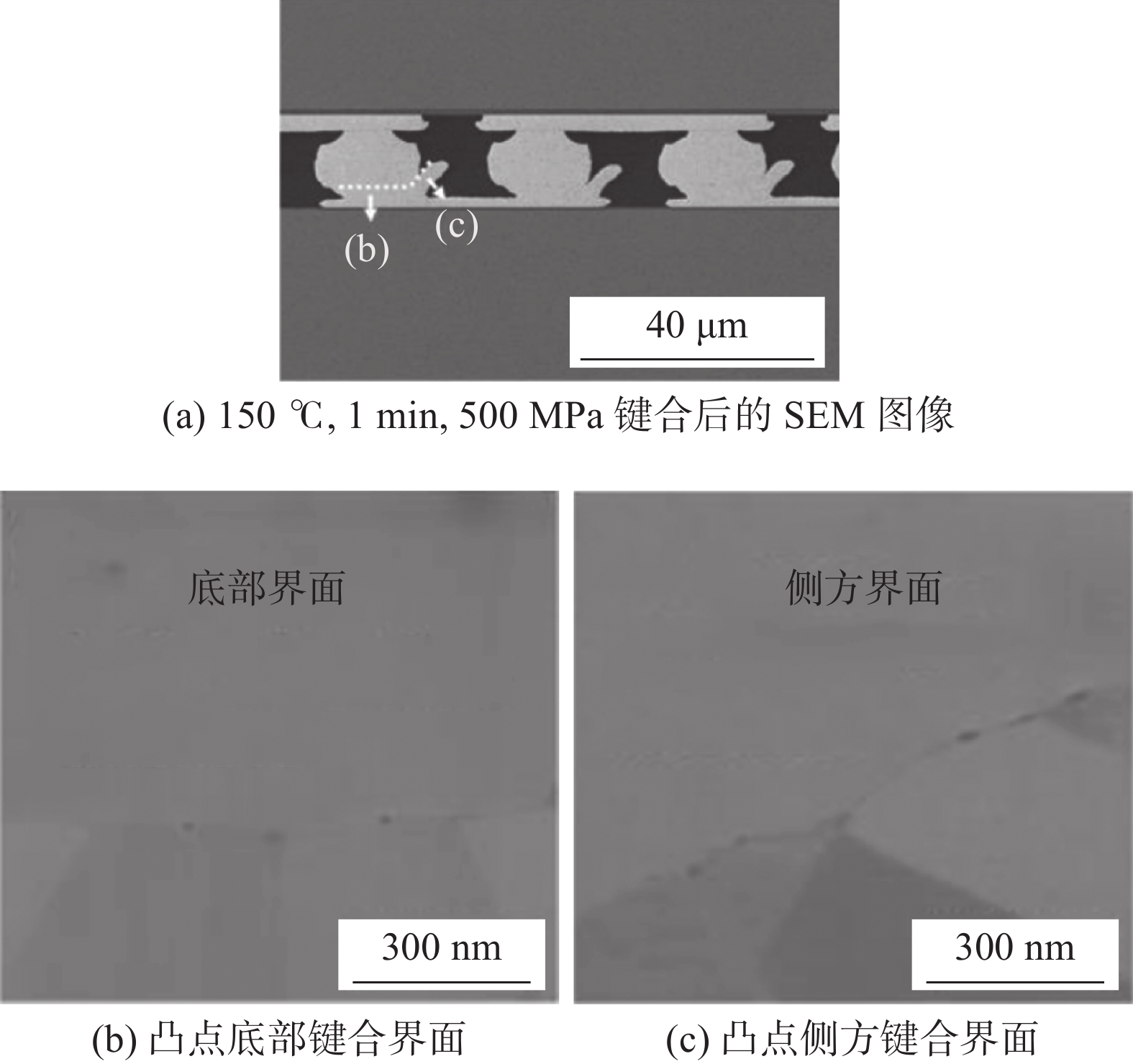

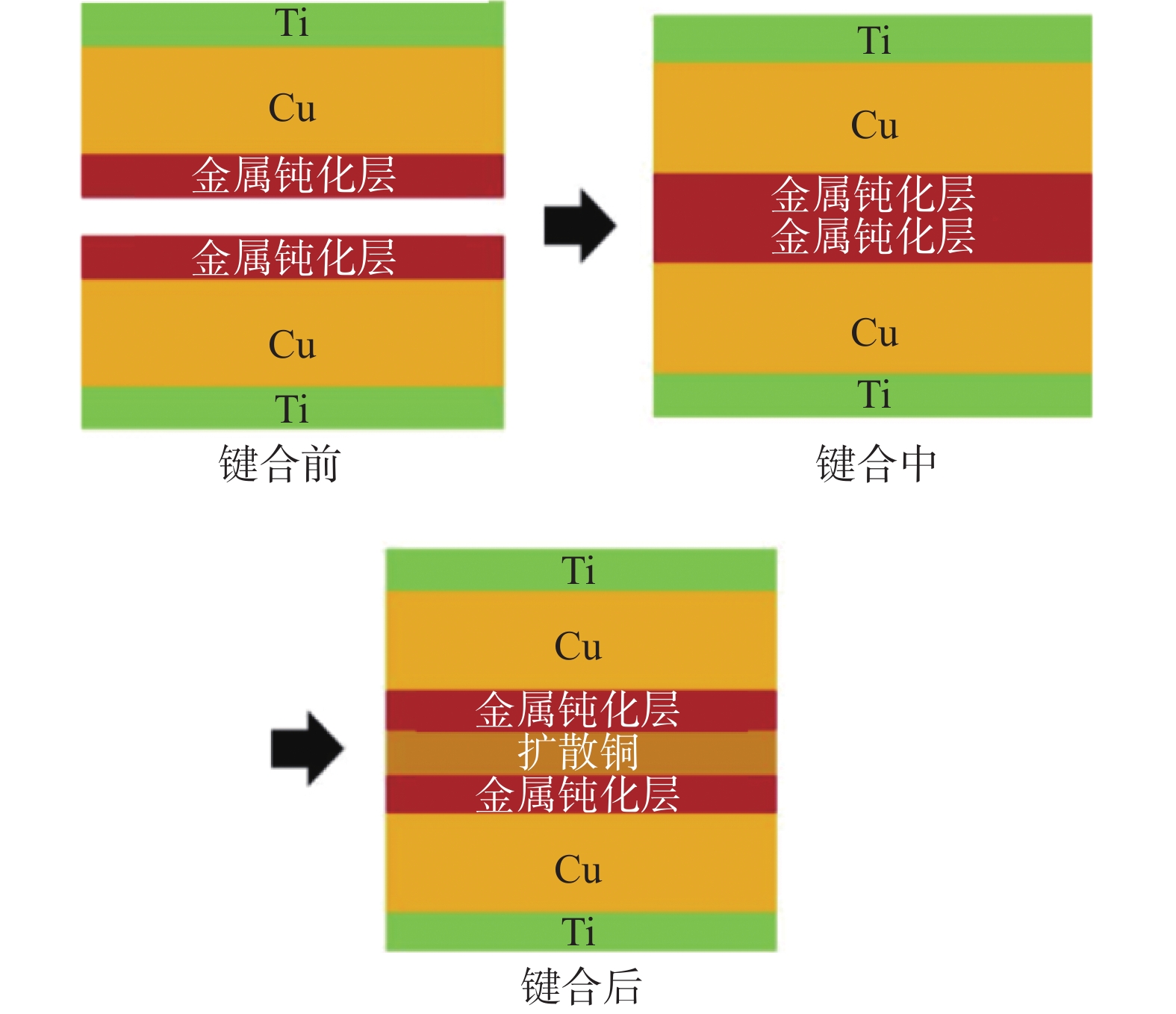

此外,研究人员提出了使用Ti[26-27],Au[28],Ag[29],Pd[30]等金属在Cu表面制作钝化层的方法,其键合原理如图7所示. Cu表面的金属钝化层及可有效防止Cu被氧化,在键合过程中金属钝化层会向Si基底一侧移动,而Cu原子会向键合界面迁移,最终完成Cu-Cu键合.

![]() 图 7 采用钝化层的Cu-Cu键合机理[30]Figure 7. Schematic of Cu-Cu bonding with passivation layer

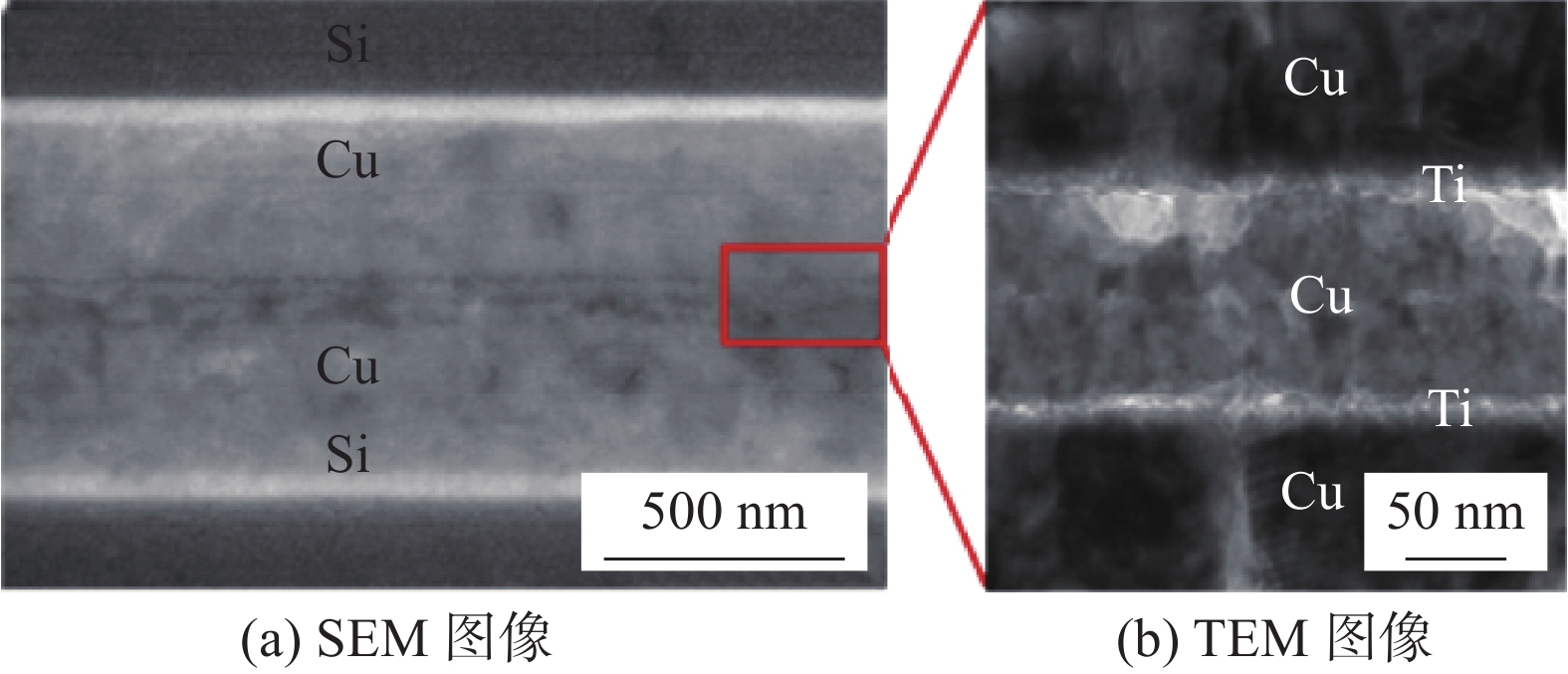

图 7 采用钝化层的Cu-Cu键合机理[30]Figure 7. Schematic of Cu-Cu bonding with passivation layer如图8为Ti作钝化层的键合结果,在180 ℃,1.91 MPa,30 ~ 50 min的键合条件下,Ti向Si基底的方向移动了约50 nm,键合界面处为Cu. 键合后经过500个TCT(−55 ~ 125 ℃)和96 h,130 ℃,85%湿度的HAST后,接头电阻无明显变化.

![]() 图 8 Ti作钝化层的键合结果[26]Figure 8. Ti passivation bonded results. (a) SEM image; (b) TEM image

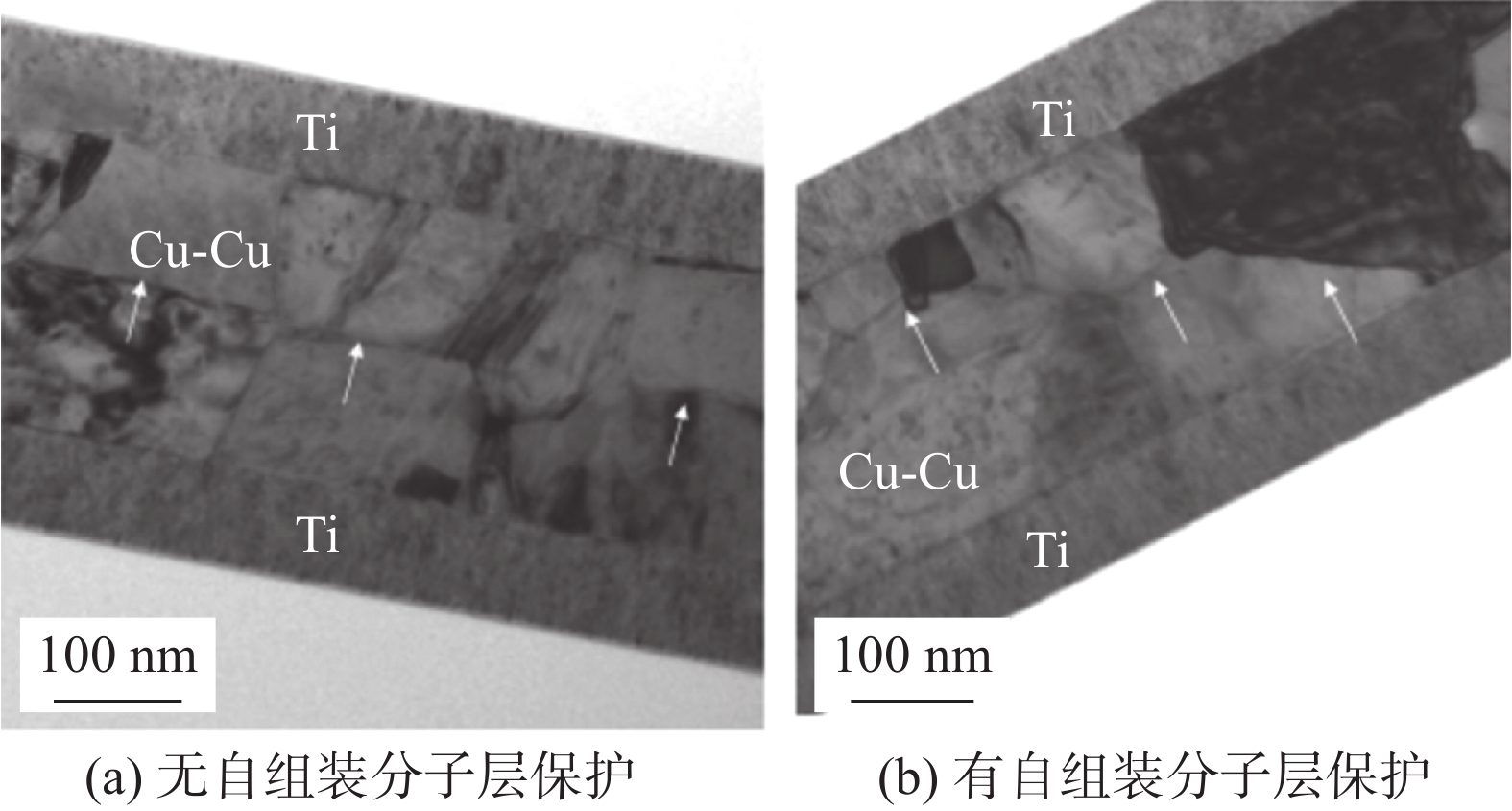

图 8 Ti作钝化层的键合结果[26]Figure 8. Ti passivation bonded results. (a) SEM image; (b) TEM image此外,Peng[31],Tan[32]等人还提出了采用自组装分子层(self-assembled monolayer,SAM)钝化Cu表面防止氧化的方法,如图9所示. 在键合前,晶圆放入烷烃硫醇溶液中进行浸泡从而在Cu表面形成钝化保护. 键合过程首先升温至250 ℃,该温度下有机物钝化层会自行分解,随后将分解产物抽走后,Cu-Cu键合过程在300 ℃,1 h,2 500 mbar真空条件下进行. 图10为无钝化保护和有自组装分子层保护的键合界面对比,可以看到无钝化保护的键合界面依然明显,而钝化保护的条件下界面基本消失.

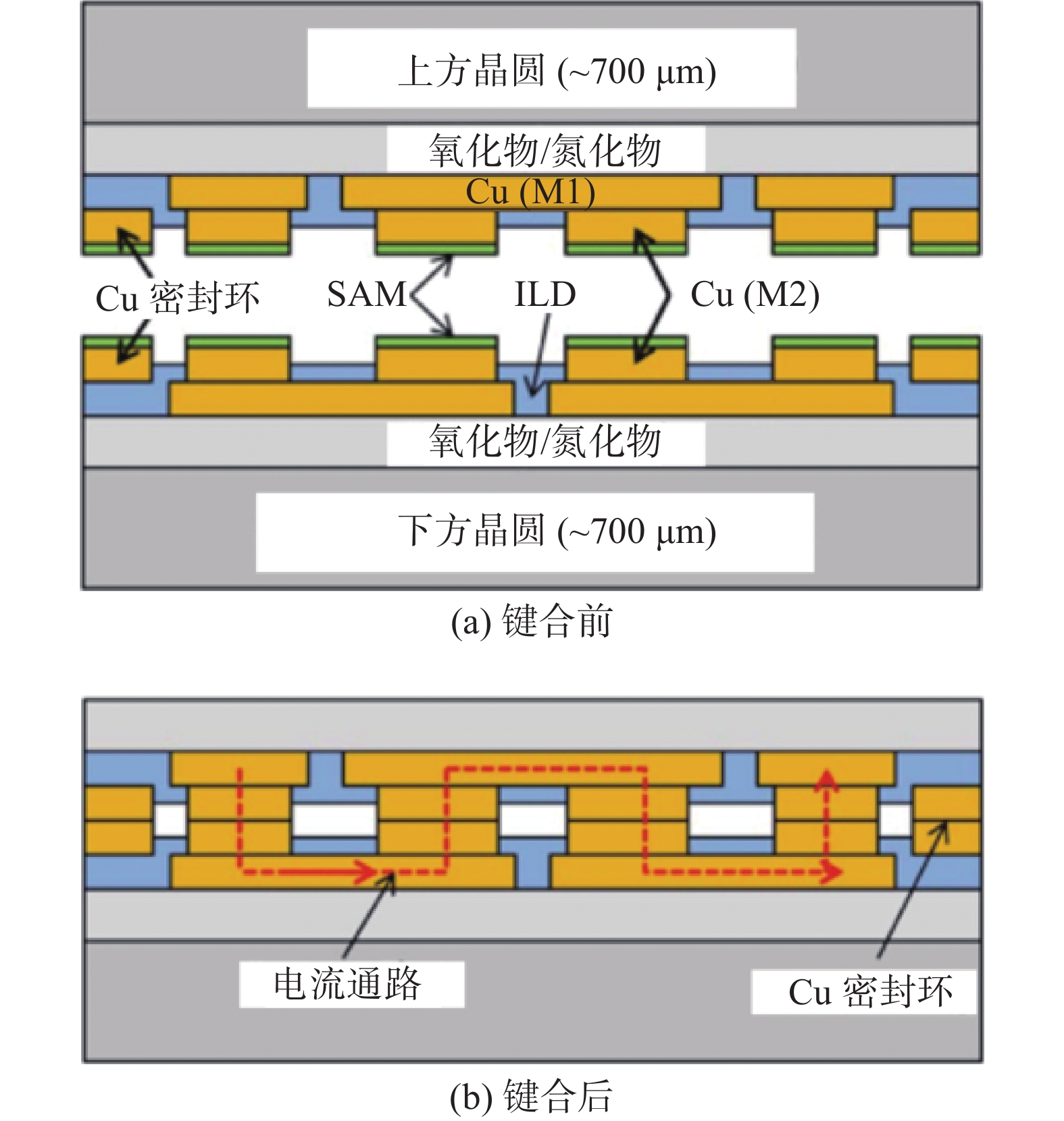

![]() 图 9 自组装分子层钝化方法的原理和工艺流程[31]Figure 9. Schematic illustration and process flow of self-assembled monolayer method. (a) before bonding; (b) after bonding

图 9 自组装分子层钝化方法的原理和工艺流程[31]Figure 9. Schematic illustration and process flow of self-assembled monolayer method. (a) before bonding; (b) after bonding![]() 图 10 Cu-Cu键合界面的TEM图像[32]Figure 10. TEM micrographs of bonded Cu layers. (a) without SAM passivation; (b) with SAM passivation

图 10 Cu-Cu键合界面的TEM图像[32]Figure 10. TEM micrographs of bonded Cu layers. (a) without SAM passivation; (b) with SAM passivation2. 混合键合工艺

窄节距互连尤其节距小于10 μm的情况下,Cu-Cu键合后的片间间隙很小,难以填充下填料. 混合键合工艺可分别实现Cu和Cu之间的键合以及Cu周围介质和介质之间的键合,键合后的介质可起到下填料的作用,减缓热应力的同时保证更高的键合强度、散热能力和防止Cu凸点被腐蚀. 典型的混合键合包括Cu/SiO2和Cu/粘结剂键合两种. Cu/SiO2混合键合的关键是得到平整度高、粗糙度小、亲水性的表面,键合前需对SiO2表面进行激活;Cu/粘结剂混合键合基于热压键合机理,Cu/热固性的粘结剂通过加热加压的方法键合在一起.

2.1 Cu/SiO2介质的混合键合

Cu/SiO2键合后可以得到无缝隙的键合界面,能有效提高热/机械可靠性[33-34]. 目前,关于Cu-Cu键合的研究很多,如前述晶面定向生长、表面钝化等,然而其中相当一部分工艺无法直接移植到Cu/SiO2混合键合. 这是因为Cu/SiO2混合键合需要综合考虑Cu-Cu及SiO2-SiO2键合,面临工艺兼容的挑战. 目前,实现Cu/SiO2混合键合的方法包括表面激活、直接键合技术(Direct Bonding Interconnect,DBI)、表面活化键合(SAB)等.

2.1.1 基于表面激活的混合键合

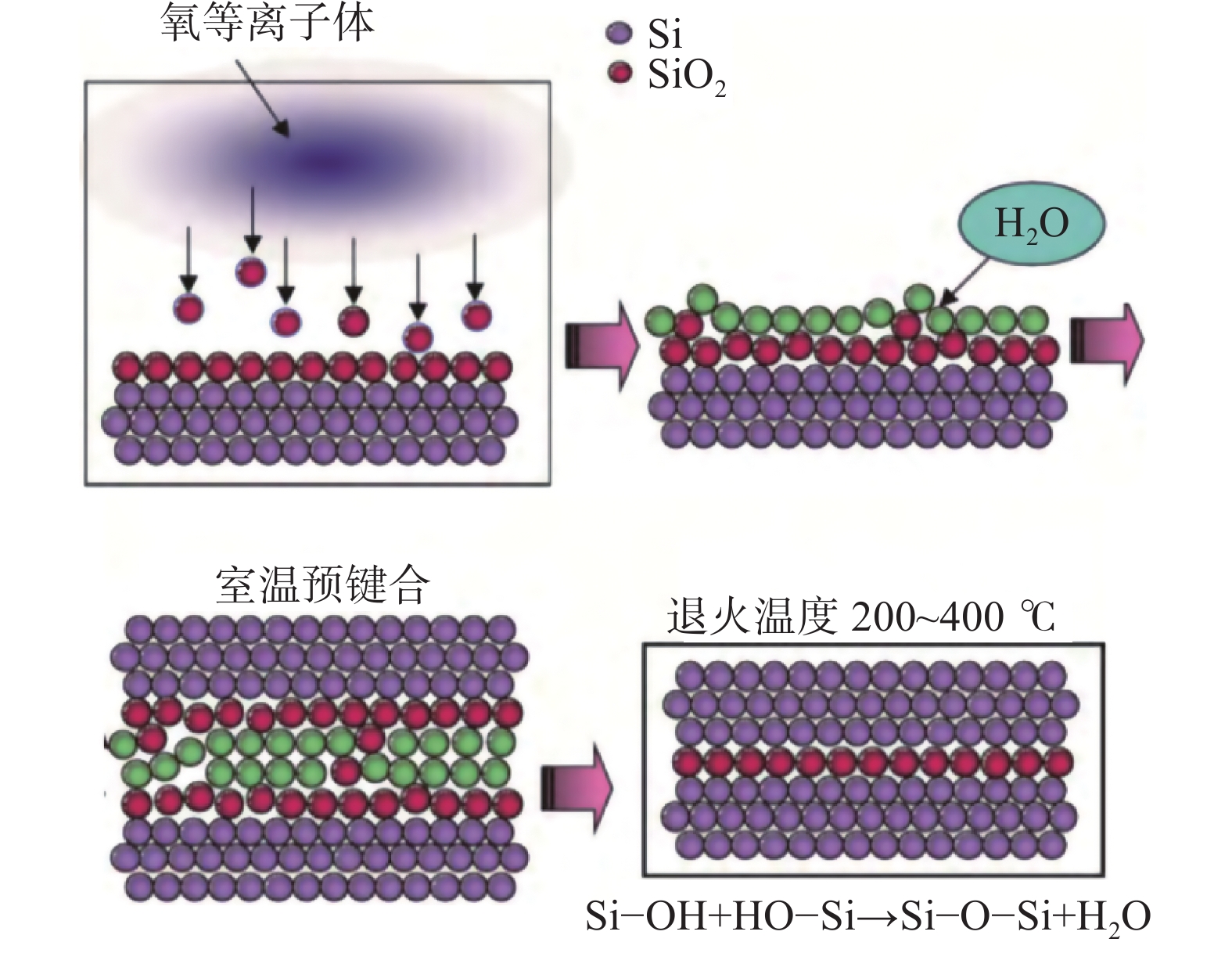

表面激活是指采用等离子体对晶圆表面进行处理,清洁晶圆表面并使其活化,研究中采用的等离子体包括O2[35],H2[36],N2[37],NH3[38],Ar[39]等. 如图11所示,等离子体活化可以提高SiO2表面的羟基密度,使得SiO2可在室温下实现亲水性预键合,并在随后200 ~ 400 ℃的退火过程中脱水达成更可靠的共价键连接[40]. 基于表面激活的混合键合的难点之一是等离子体处理会对Cu表面产生不利影响,例如使用O2等离子体会氧化Cu,即便是Ar等离子体处理时腔体内含有的氧也会对Cu表面造成氧化[39];使用N2,NH3等处理会使得Cu表面生成氮化物[37-38],影响Cu-Cu键合.

![]() 图 11 等离子体活化键合的原理[40]Figure 11. Schematic of plasma activated bonding

图 11 等离子体活化键合的原理[40]Figure 11. Schematic of plasma activated bonding2.1.2 基于DBI的混合键合

Co[41],Enquist[42]等人提出了DBI的混合键合方法[41-42],其具体工艺流程如图12所示. 首先通过溅射、电镀等半导体工艺在晶圆表面制作Cu凸点,随后沉积SiO2介质层覆盖Cu凸点及晶圆表面,接着使用标准CMP工艺露出晶圆表面的Cu焊盘并对焊盘和SiO2介质进行整平. 在CMP过程中,抛光液作用于Cu表面使其高度略低于SiO2表面. 在键合前使用等离子体对SiO2表面进行激活,使其可在室温、无压条件下完成预键合.预键合后需要在300 ~ 350 ℃下进行退火,退火可以提高SiO2-SiO2之间的键合强度,并使得Cu焊盘高温膨胀相互挤压,完成Cu-Cu键合. 图13为键合后的界面,Cu-Cu及SiO2-SiO2键合界面都没有缝隙存在. DBI由于在室温下完成预键合,所以可以保证很高的对中精度,报道称其可实现3 μm的互连节距. DBI具有良好的可靠性,键合后经过2 000个TCT(−40 ~ 150 ℃)和2 000 h,275 ℃的高温存储后,接头电阻分别下降了1.2% ~ 1.7%和1.2% ~ 1.4%,满足相关标准中电阻升高小于10%的要求[43].

![]() 图 12 DBI流程示意图[41]Figure 12. DBI technology process flow

图 12 DBI流程示意图[41]Figure 12. DBI technology process flow![]() 图 13 DBI键合后的界面SEM图像[42]Figure 13. SEM image of bonded interface by DBI method

图 13 DBI键合后的界面SEM图像[42]Figure 13. SEM image of bonded interface by DBI method2.1.3 基于SAB的混合键合

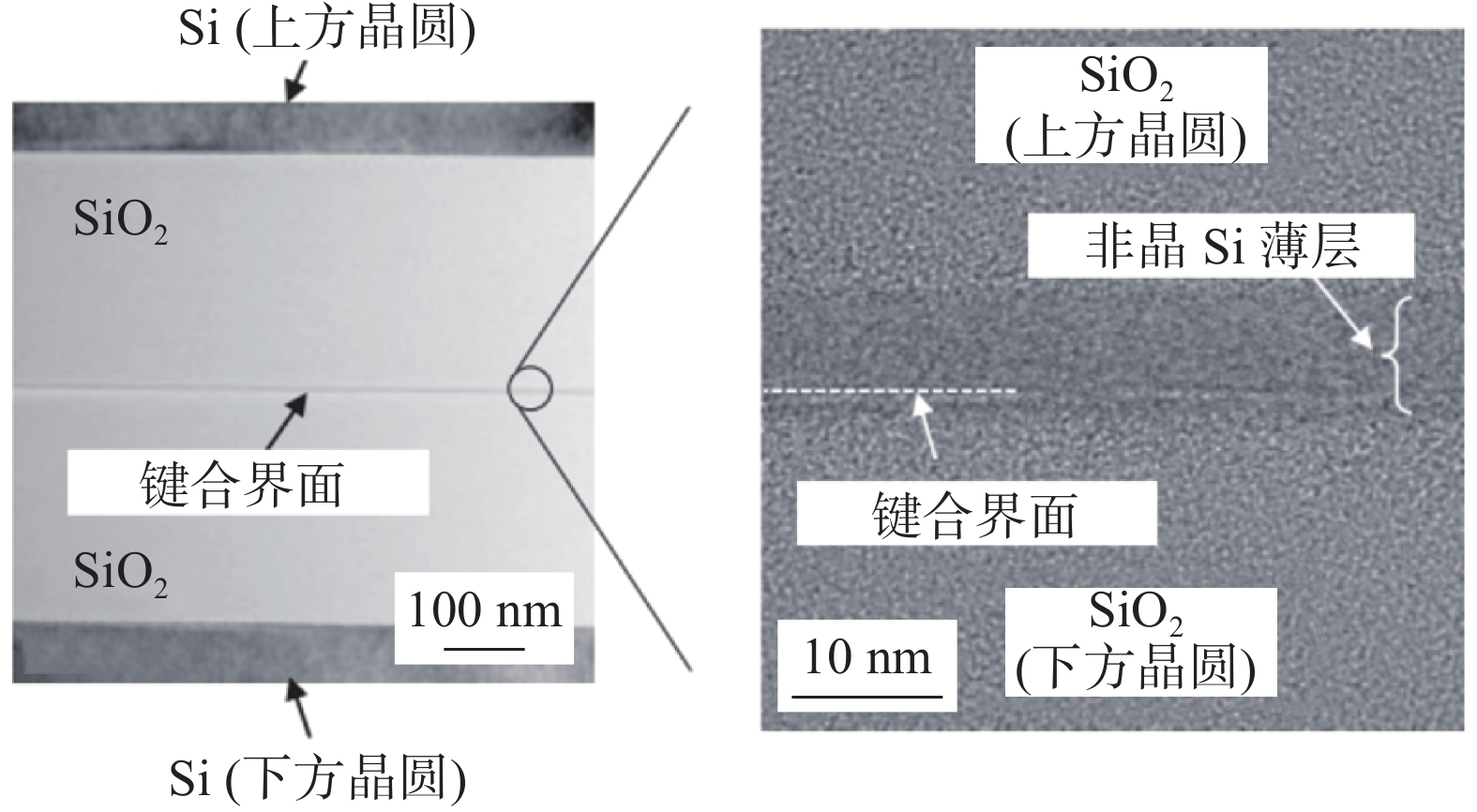

Utsumi[44-45]等人提出了一种基于Ar等离子体的SAB混合键合方法. 此前研究中发现,超高真空下采用Ar等离子体轰击可以实现Cu-Cu,Si-Si之间的键合,但对SiO2-SiO2之间的键合效果较差. 为了提高SiO2-SiO2之间的键合质量,研究人员在SiO2表面溅射了约12 nm的Si作为中间层,随后经过SAB处理并在室温下键合. TEM观察发现,键合后的界面为厚度约7 nm的非晶Si薄层(如图14所示),键合强度约为25 MPa. 这种方法也会在Cu表面引入Si层,在一定程度上降低Cu的导电性.

![]() 图 14 Si作为SiO2-SiO2室温键合的中间层[44]Figure 14. Bonding of SiO2 and SiO2 at room temperature using Si ultrathin film

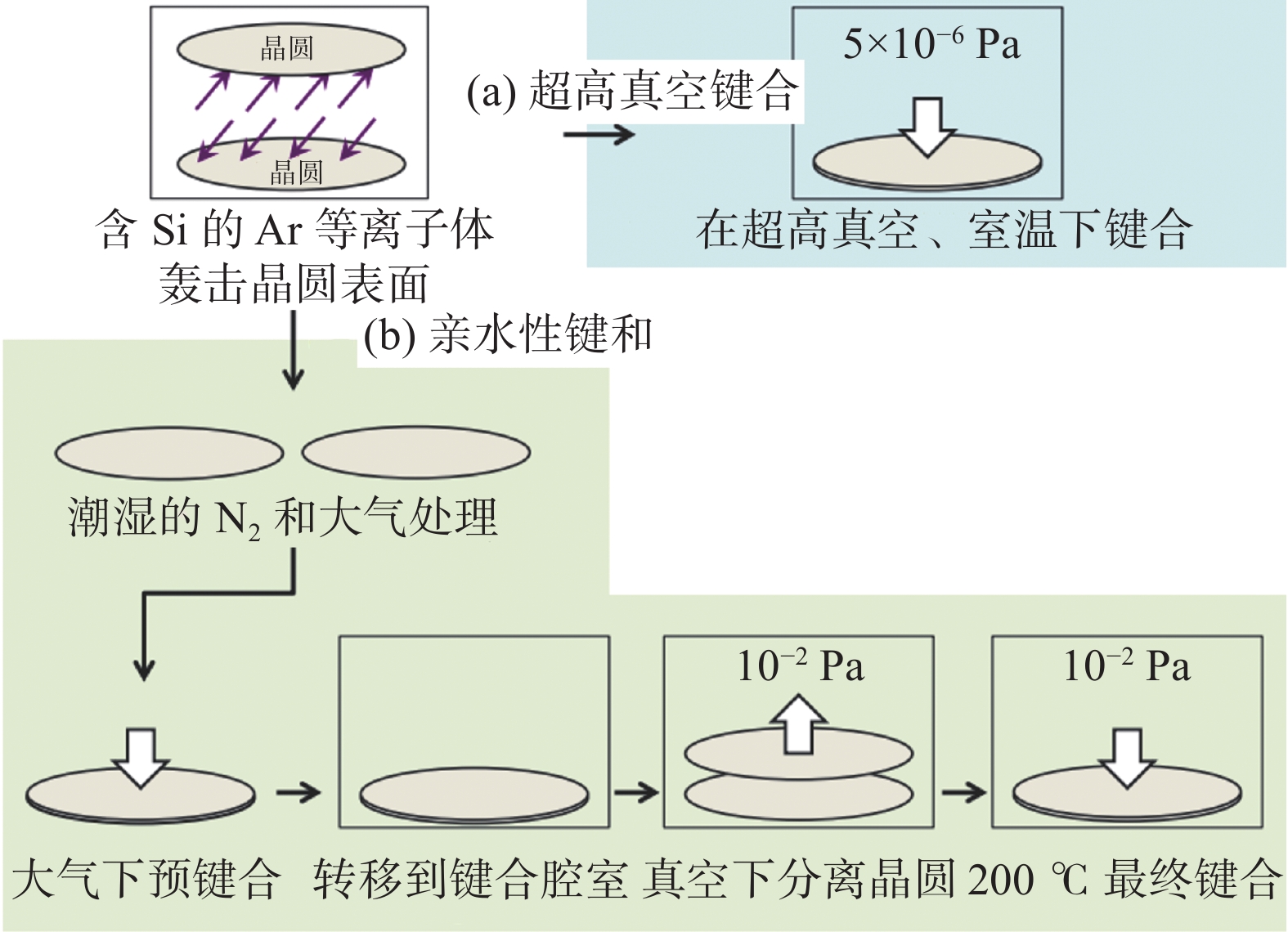

图 14 Si作为SiO2-SiO2室温键合的中间层[44]Figure 14. Bonding of SiO2 and SiO2 at room temperature using Si ultrathin film进一步地,He等人[46]提出了采用含Si的Ar等离子体处理待键合表面的工艺方法[46],如图15所示. 含Si等离子体可提高SiO2表面的Si点位,促进SiO2-SiO2键合. 表面处理后分两条工艺路线进行晶圆键合,一种是直接在5 × 10−6 Pa的高真空下直接进行室温键合,另一种为采用预键合-分离-最终键合的多步路线进行亲水性键合:(1)将处理后的晶圆置于真空度为2 × 10−2 Pa的腔室内,随后向腔室内充入潮湿的N2至3 kPa,接着冲入干燥氮气至大气压,晶圆取出后采用纯水冲洗并甩干;(2)在大气(湿度约为40%)、常温、无压条件下对晶圆进行预键合,并在大气下保存10 min以上;(3)将预键合后的晶圆转移至键合腔室内,并在10−2 Pa的条件下分离预键合的晶圆;(4)在10−2 Pa真空度,200 ℃,2.5 MPa,30 min的条件下进行最终键合并在大气压下200 ℃退火2 h. 强度测试表明,预键合—分离—最终键合的方法可实现2.0 ~ 2.5 J/m2结合能的SiO2-SiO2键合,优于高真空直接键合的0.5 J/m2. 这是由于该方法可以在最终键合前增加−OH吸附及去除表面H2O分子,更有利于提高键合强度、减少界面空洞. 此外,这种方法也可以得到低含氧量的Cu-Cu键合界面.

![]() 图 15 基于SAB的混合键合流程示意图[46]Figure 15. Process flow of the combined SAB with (a) UHV bonding and (b) hydrophilic bonding

图 15 基于SAB的混合键合流程示意图[46]Figure 15. Process flow of the combined SAB with (a) UHV bonding and (b) hydrophilic bonding2.2 Cu/粘结剂介质的混合键合

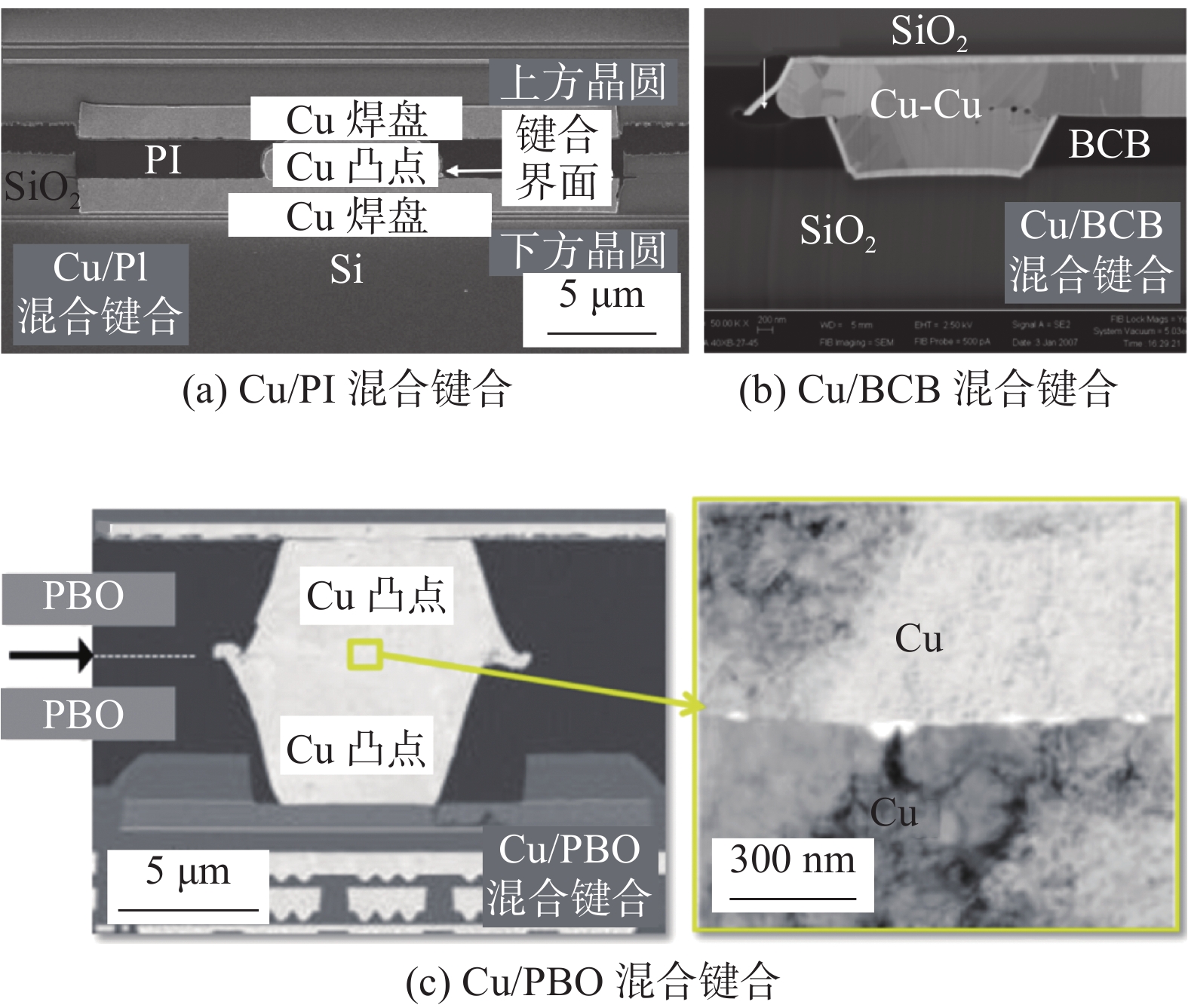

Cu/粘结剂介质的混合键合与Cu/SiO2混合键合类似,只是使用粘结剂如BCB[47],PBO[48],PI[49]等替代了SiO2介质(图16),粘结剂具有更好的柔性,可以一定程度上容忍介质表面的微尘颗粒物.

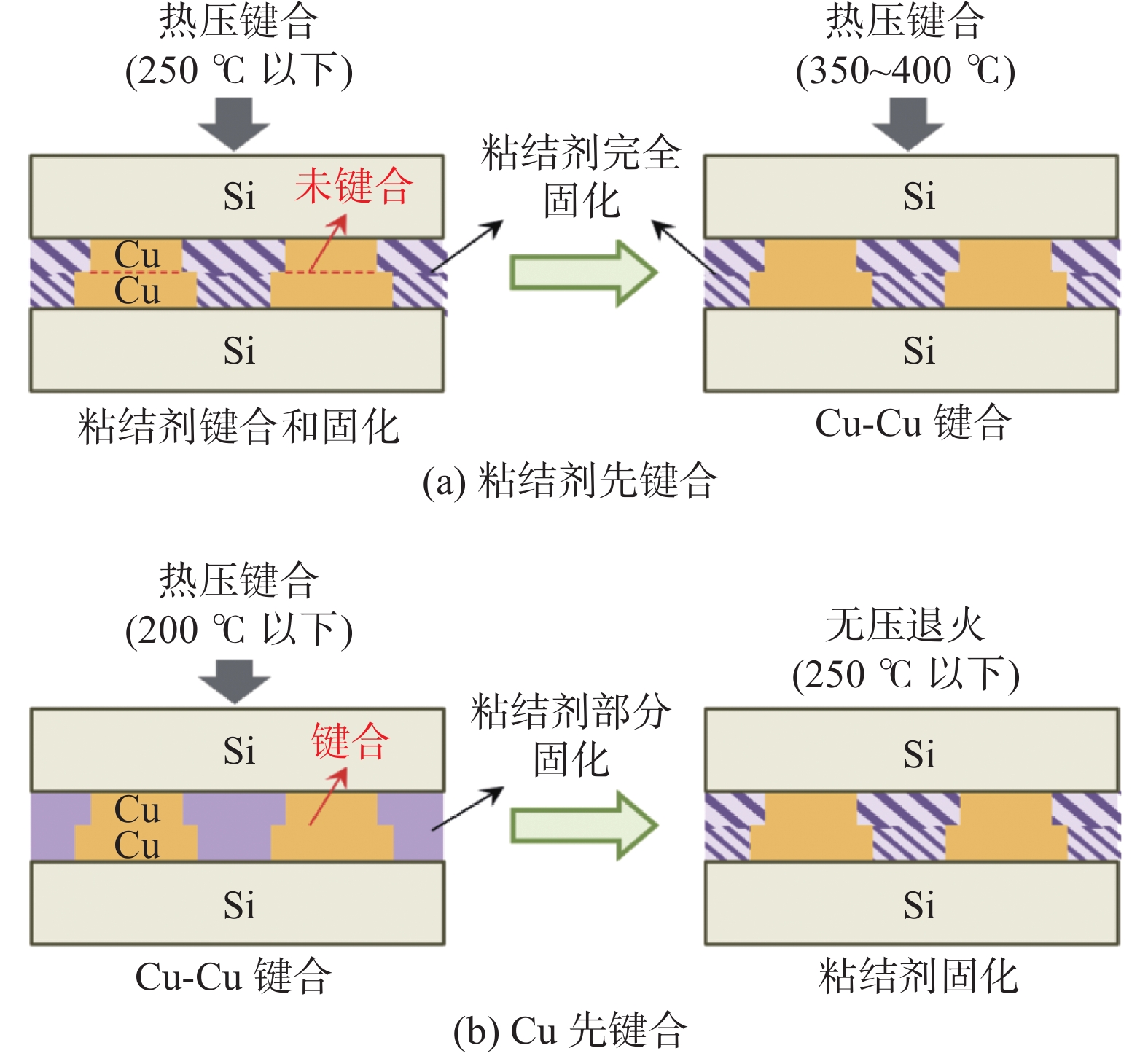

Cu/粘结剂混合键合主要基于热压的方法,实现方式包括两种:①粘结剂先键合[47],如图17a所示. 在较低的温度下(约250 ℃,取决于粘结剂的种类)首先将粘结剂键合并固化,此时Cu-Cu尚未完成键合,然后在更高的温度(350 ~ 400 ℃)下进行热压实现Cu-Cu键合,粘结剂在低温下键合可以防止更高的Cu键合温度对未固化的粘结剂造成损伤. 不过这种方法存在诸多不足,如需选择耐高温的粘结剂材料、粘结剂需要较长的固化时间导致键合效率降低等. ② Cu先键合[50],如图17b所示. Cu首先在低于粘结剂固化的温度下短时键合(如≤10 min),随后在更高的温度下对粘结剂进行固化且进一步提高Cu-Cu键合的强度. 实现Cu-Cu低温键合的方法需要考虑到对粘结剂表面的影响,如Ar原子束和Ar等离子体处理虽然可以降低Cu-Cu键合的温度,但激发出来的金属离子却会污染粘结剂表面,干扰粘结剂的键合[51]. 为此,有研究人员采用Pt催化后含H的甲酸对Cu和粘结剂表面进行处理[50],可以在200 ℃,5 min条件下完成Cu-Cu键合,并且不会对粘结剂键合产生不利影响.

![]() 图 17 Cu和粘结剂混合键合方式[50]Figure 17. Cu/adhesive hybrid bonding. (a) “adhesive-first” hybrid bonding process; (b) “Cu-first” hybrid bonding process

图 17 Cu和粘结剂混合键合方式[50]Figure 17. Cu/adhesive hybrid bonding. (a) “adhesive-first” hybrid bonding process; (b) “Cu-first” hybrid bonding process3. 热压键合和混合键合的工艺难点

前述分别汇总了Cu-Cu热压键合、混合键合方法的研究现状. 目前大部分研究还仅仅停留在实验室阶段,需要进一步深入对工艺和机理的探讨. 与此同时,当前这些方法也面临着共性的工艺难点,包括以下两方面:

3.1 工艺要求非常苛刻

无论是热压键合还是混合键合方法对待键合表面的质量如粗糙度、光洁度、晶圆整体翘曲程度有很高要求. 由于制作完成的Cu表面为粗糙状态且有一定的高度差,需要经过昂贵、复杂的CMP、飞行切割等整平工艺对待键合表面进行平坦化,降低表面粗糙度和高度差. 此外,晶圆本身还具有一定的翘曲,尤其是面积大、厚度薄的晶圆,翘曲程度会更加明显[3],Cu-Cu键合的“硬碰硬”接触方式易在键合良率方面出现问题. 在低温互连方面,为了实现300 ℃以下的低温互连,增大界面接触面积,往往需要增加键合压力至100 MPa以上,这样大的压力可能会导致晶圆碎裂或介质层开裂、变形等问题,不能满足工艺要求. 此外,混合键合中Cu-Cu键合和介质-介质键合二者常常会相互干扰,需要兼顾两方面的键合要求,对材料、工艺都提出了很大挑战.

3.2 难以灵活适用于2.5D互连

Cu/介质混合键合技术近年来发展迅速,部分混合键合技术已在实际制造中应用于3D互连的晶圆键合(Wafer to Wafer,W2W)[52]. 然而,混合键合技术对待键合表面的微尘颗粒物很敏感. 即便如Cu-粘结剂混合键合可以容忍一定的微尘颗粒物,但如果颗粒物出现在Cu表面,仍会严重影响键合质量. 在2.5D互连的芯片-晶圆键合(Chip to Wafer,C2W)场合中,晶圆需要切割成单个芯片再键合到载板晶圆表面,切割过程中不可避免地会引入微颗粒物等,混合键合技术难以适用. 此外,2.5D互连主要是为了实现芯片功能整合,需要贴装的芯片种类非常多样化,往往来自不同晶圆制造厂商,下游的封装厂很难说服上游晶圆厂改变制程来适应混合键合的工艺需求.

4. Cu纳米材料烧结连接

近年来,基于Cu纳米材料烧结连接实现Cu-Cu键合逐渐获得关注. 与热压键合和混合键合相比,纳米材料烧结对待键合表面的粗糙度、平整度等有更高的适应性,能够大幅降低工艺要求.

4.1 纳米材料烧结连接的基本原理

纳米材料相对于宏观块体材料,表面原子占比增多,具有更高的表面能[53],更易发生原子扩散,非常有利于在低温下进行烧结连接.

以金属纳米颗粒为例,其烧结过程可以用经典粉末烧结理论进行描述. 根据粉末烧结理论,由粉末材料构成的颗粒系统在烧结时倾向于降低其表面的自由能,这是推进烧结进程的主要动力,烧结颈的长大是烧结过程进行的具体表现. 在烧结过程中,首先分散/疏松的纳米颗粒在压力作用下相互接触,然后随着温度的升高发生表面扩散、晶界扩散、晶内扩散,烧结颈逐渐长大,组织趋于致密化. 烧结后的组织为多孔结构,与块体材料相比具有更小的模量,更容易发生塑性变形,对粗糙、不平整表面有优异的“填补”效应[54],具有更宽的工艺窗口.

根据纳米材料烧结前的形态进行划分,研究中的Cu纳米材料主要包括三类:纳米线、纳米多孔骨架和纳米颗粒. 下面分别对这三方面的研究现状进行简要介绍.

4.2 Cu纳米线烧结

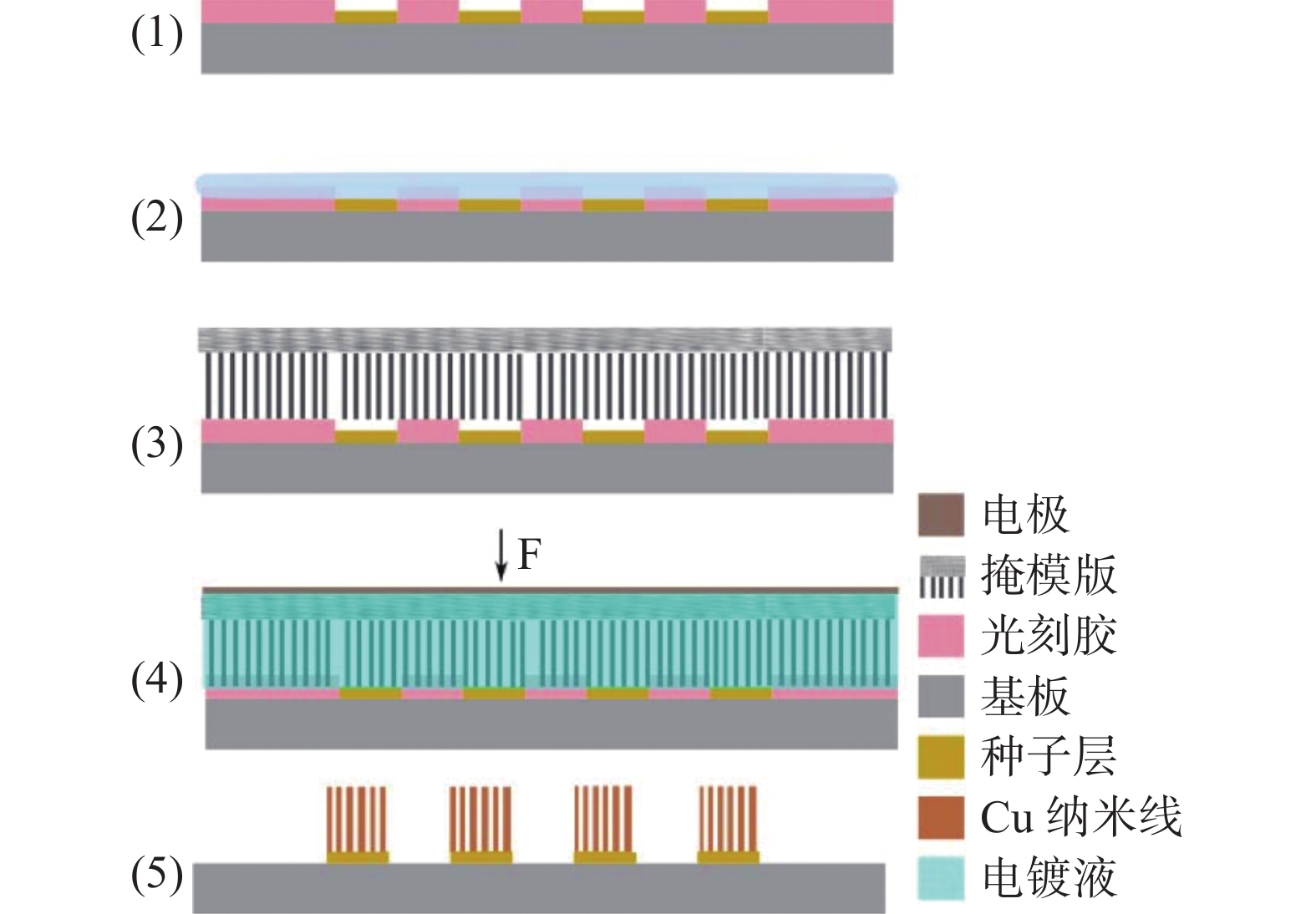

Roustaie[55-56],Strahringer[57],Yu[58]等人提出了一种基于Cu纳米线烧结的工艺,该工艺的优势主要体现在其Cu纳米线阵列的图形化方式与成熟半导体工艺良好兼容,可实现高密度Cu纳米线凸点的制备. 具体工艺流程如图18所示:①在对晶圆进行厚胶光刻漏出Cu焊盘,Cu焊盘作为纳米线生长的基底,光刻胶作为纳米线定向生长的掩膜;②通过氧等离子体轰击去除Cu焊盘表面的有机物残留;③将带有直孔阵列的特制掩模板压覆在晶圆表面,并与Cu焊盘接触,整体浸没到Cu电镀液中;④随后进行电镀工艺,电镀过程中Cu纳米线以Cu焊盘为基底,沿着掩模版孔阵列的方向向上生长;(5)最后去除掩模版,获得由Cu纳米线构成的凸点阵列.

![]() 图 18 制备晶圆级窄节距纳米线阵列[55]Figure 18. Nanowiring of fine pitch pads on a wafer

图 18 制备晶圆级窄节距纳米线阵列[55]Figure 18. Nanowiring of fine pitch pads on a wafer这种方法可以实现凸点阵列的晶圆级制备,如图19a,b所示. 所获得的Cu纳米线阵列可以在230 ℃,60 MPa的温度、压力条件下实现57.4 MPa的剪切强度,且经过1 000个热循环测试(−40 ~ 150 ℃)和4 000 h的HAST测试(85 ℃,85%湿度)后剪切强度无明显下降.

![]() 图 19 键合前后的Cu纳米线[56]Figure 19. Cu nanowires before and after bonding. (a) entire wafer covered with Cu nanowires; (b) 5 μm pads with 10 μm pitch; (c) cross sections of about 60 μm and; (d) 10 μm pitch connected with nanowires

图 19 键合前后的Cu纳米线[56]Figure 19. Cu nanowires before and after bonding. (a) entire wafer covered with Cu nanowires; (b) 5 μm pads with 10 μm pitch; (c) cross sections of about 60 μm and; (d) 10 μm pitch connected with nanowires4.3 Cu纳米多孔骨架烧结

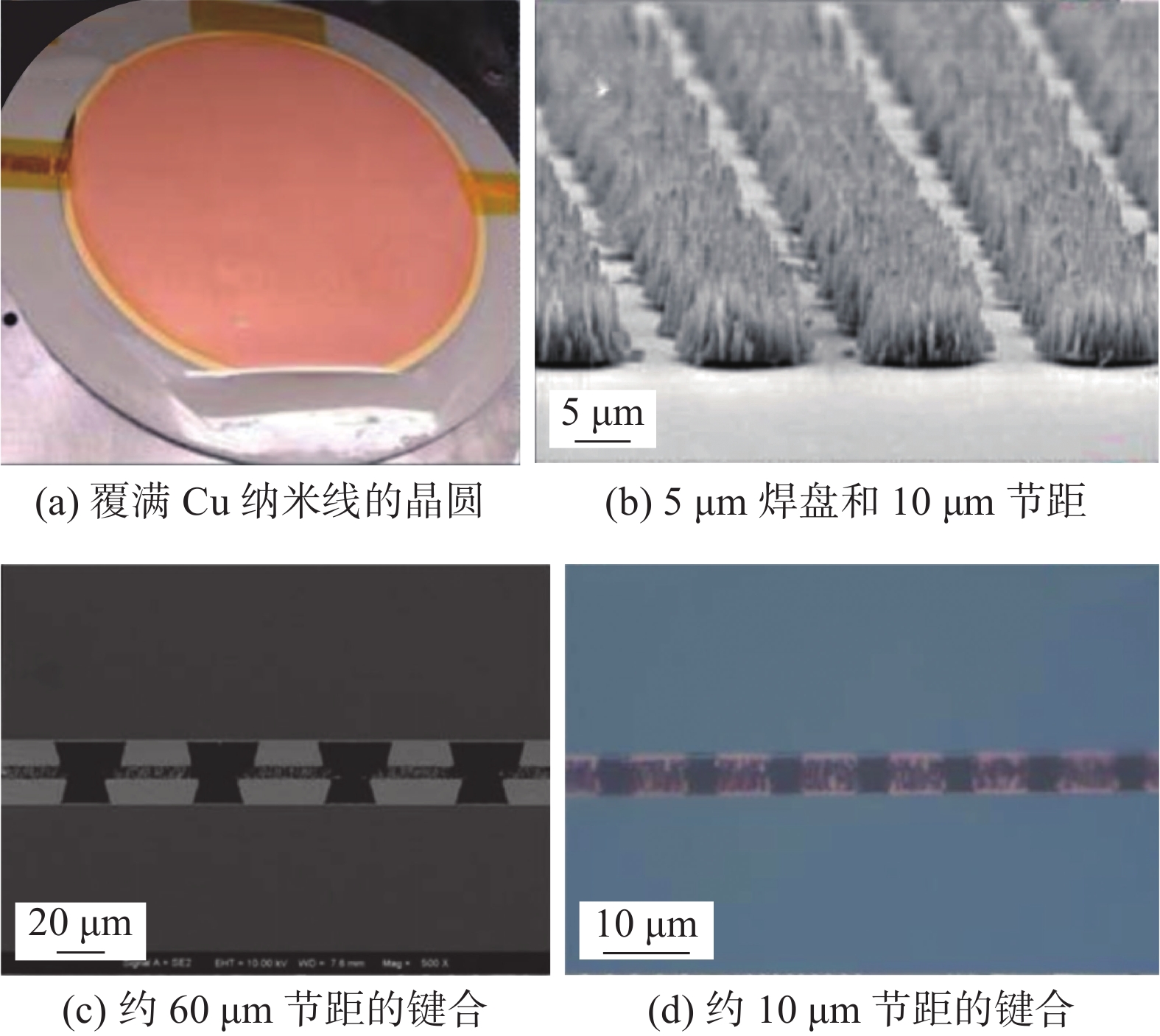

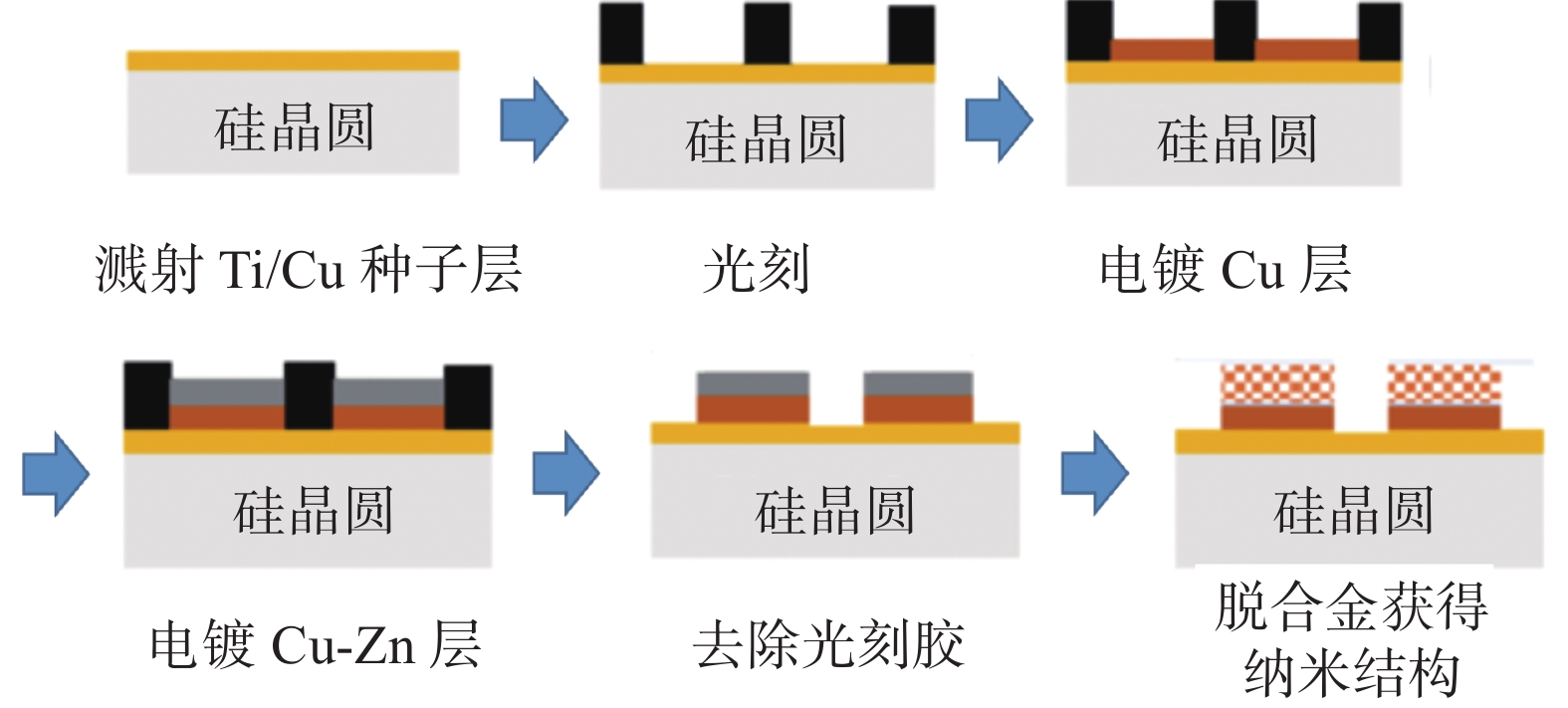

Shahane[59, 61],Sosa[60, 63],Mohan[62]等人提出了一种可图形化的脱合金法制备Cu纳米多孔骨架凸点[59-63],其具体工艺流程如图20所示. 首先在晶圆表面溅射一层Ti/Cu作为后续电镀工艺的种子层,随后旋涂光刻胶并进行光刻得到所需的孔阵列图案,接着在光刻胶孔内分别电镀4 ~ 8 μm厚的Cu凸点和5 ~ 10 μm厚的Cu-Zn合金,光刻胶去除后即可得到上方为Cu-Zn合金、下方为Cu的复合凸点结构,最后使用1%质量分数的HCl在室温下腐蚀4 h使得Cu-Zn合金中的Zn被腐蚀并获得Cu纳米多孔骨架凸点.

![]() 图 20 Cu纳米多孔骨架的图形化路线[62]Figure 20. Process flow for fabrication of patterned np-Cu foam films

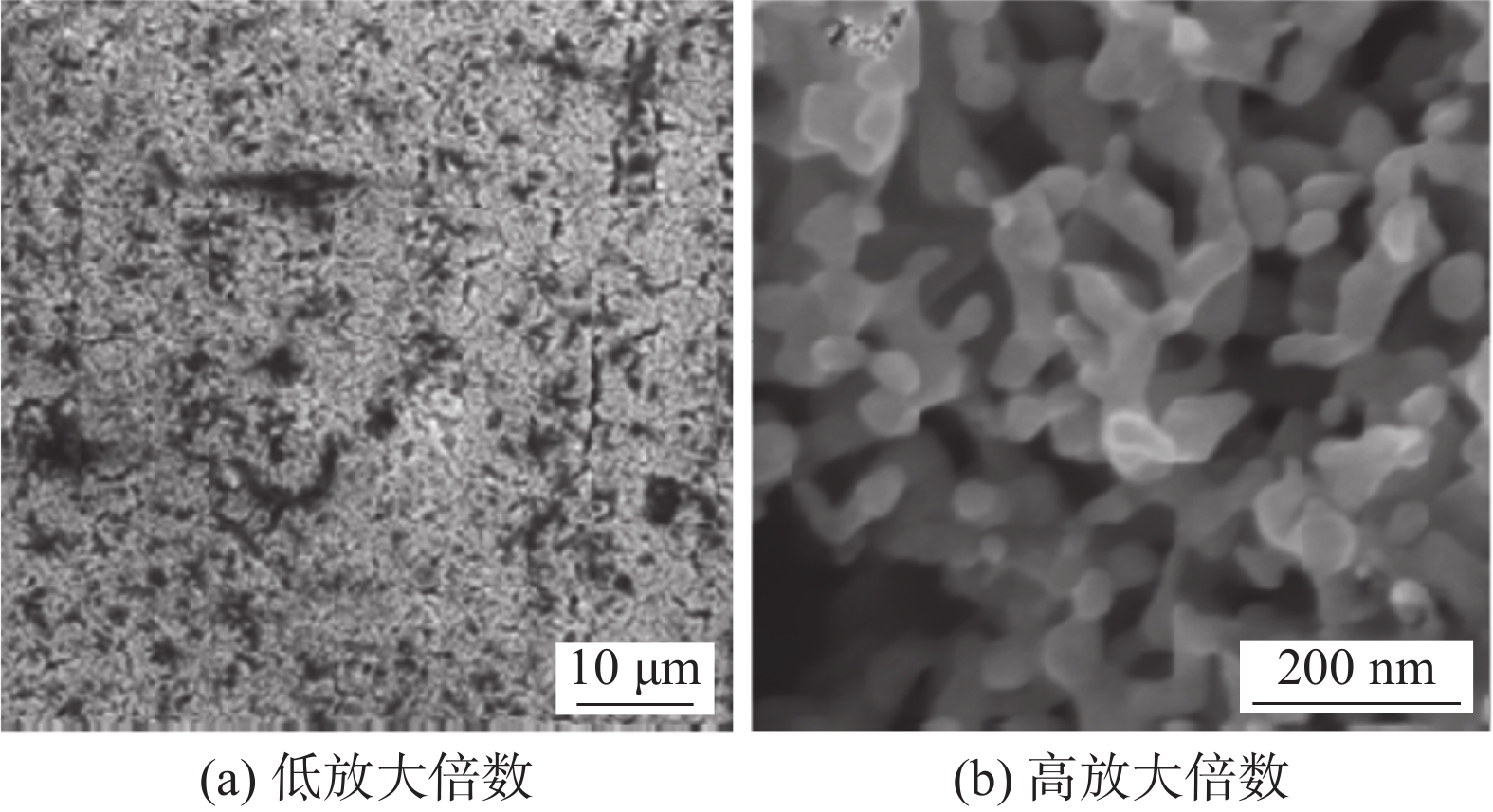

图 20 Cu纳米多孔骨架的图形化路线[62]Figure 20. Process flow for fabrication of patterned np-Cu foam films在Cu纳米多孔骨架制备方面,研究人员主要研究了电流密度、Cu-Zn合金中Zn的含量、退火工艺对Cu纳米多孔骨架组织的影响,结果表明在电流密度为2.75 mA/cm2、Zn含量为85%、200 ℃/30 min/N2退火的工艺条件下,可以获得较理想的纳米多孔结构,如图21所示,特征尺寸在60 nm以下,其中约有10%的Zn残留.

![]() 图 21 纳米多孔骨架的组织形态[62]Figure 21. Morphology of dealloyed np-Cu foam film. (a) low magnification; (b) high magnification

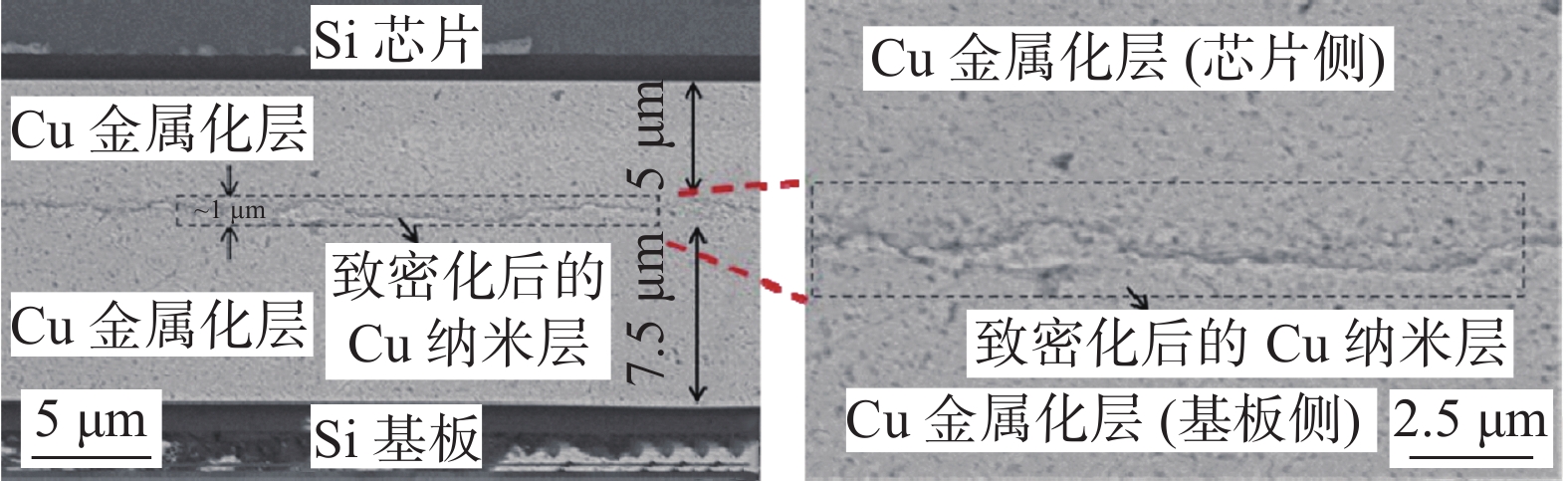

图 21 纳米多孔骨架的组织形态[62]Figure 21. Morphology of dealloyed np-Cu foam film. (a) low magnification; (b) high magnification在250 ℃,9 MPa,30 min,5%甲酸气氛的键合条件下,剪切强度可达47 MPa. 如图22所示,键合前约3 ~ 4 μm厚的多孔纳米结构被压缩到了1 μm以内,这表明该方法可以在一定程度上通过塑性变形弥补基板翘曲以及Cu柱高度差带来的不平整度. 不过,该工艺制备获得的Cu多孔结构中存在一定的Zn残余,活泼金属对长期服役可靠性的影响需要进一步研究.

![]() 图 22 250 ℃/9 MPa/30 min烧结条件下的键合界面[62]Figure 22. Cross-sectional images of the sintered joint under the condition of 250 ℃/9 MPa/30 min

图 22 250 ℃/9 MPa/30 min烧结条件下的键合界面[62]Figure 22. Cross-sectional images of the sintered joint under the condition of 250 ℃/9 MPa/30 min4.4 Cu纳米颗粒烧结

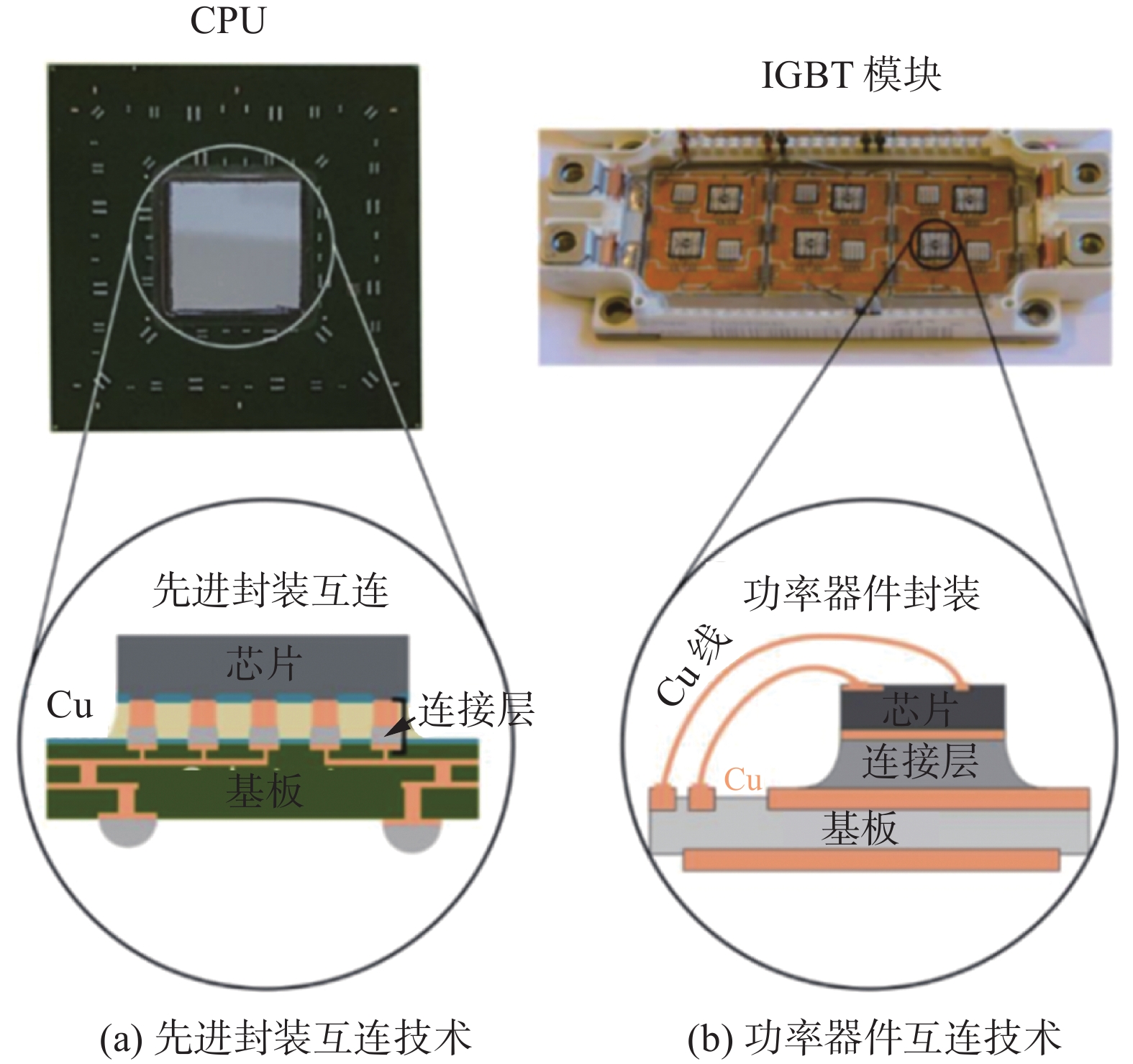

目前,Cu纳米颗粒用于烧结连接主要是通过配置成铜纳米焊膏并应用于功率器件封装[64-66]. 如图23所示,功率器件封装的芯片与基板间一般只有一个互连层,而先进封装互连的焊点数量成千上万. Cu纳米焊膏应用于先进封装互连的难点之一是图形化,即如何制作出大规模焊点阵列.

![]() 图 23 不同互连技术的示意图[67]Figure 23. Schematic of different packaging technology. (a) advanced packaging technology; (b) power device packaging technology

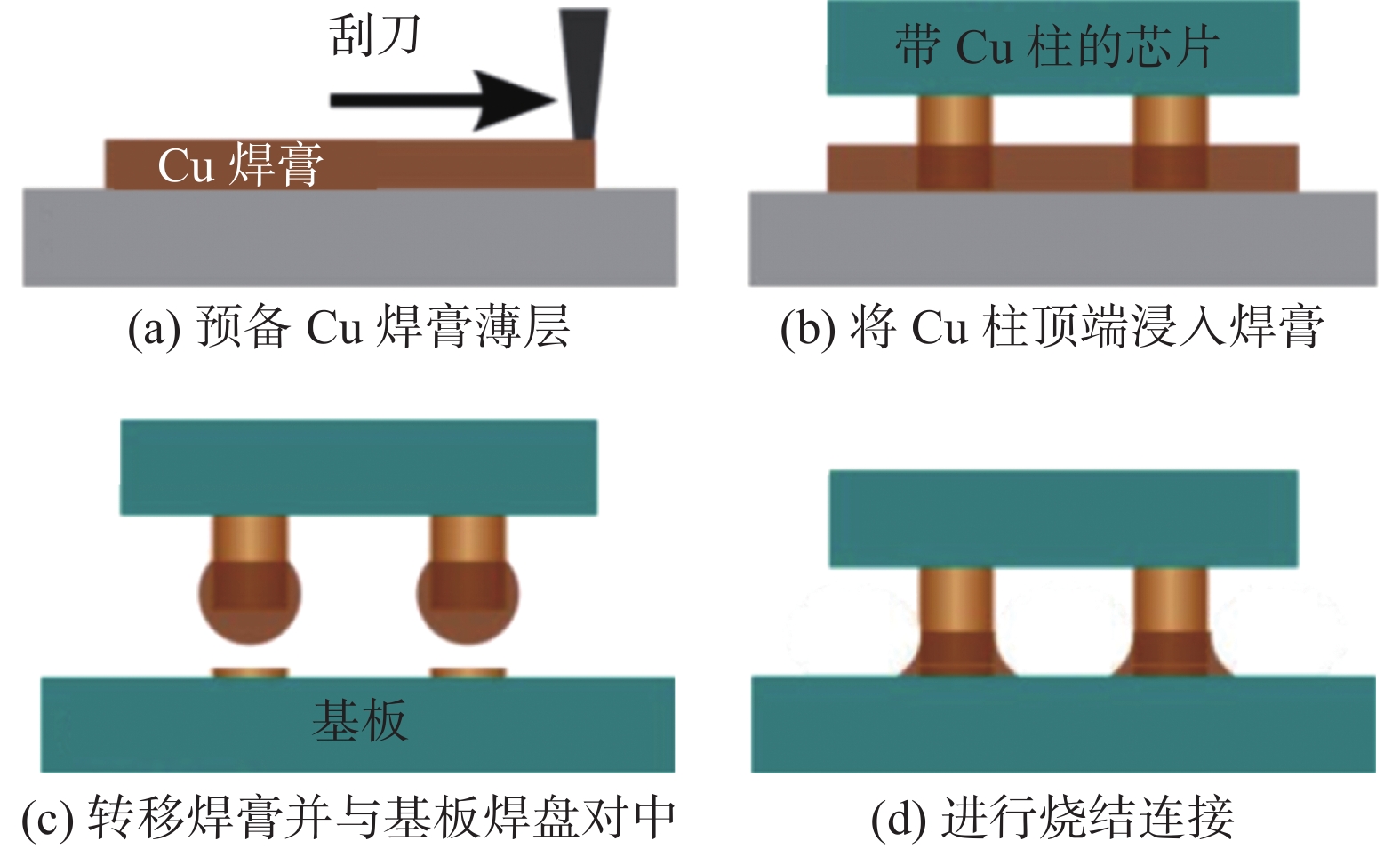

图 23 不同互连技术的示意图[67]Figure 23. Schematic of different packaging technology. (a) advanced packaging technology; (b) power device packaging technologyDel Carro[67-69],Zürcher[70-71]等人提出了一种浸蘸转移的方法实现焊膏图形化,其具体流程如图24所示. 首先将微纳米颗粒混合的Cu焊膏通过刮刀刮平获得约20 μm厚度的薄层,将电镀有Cu凸点的芯片在焊膏中浸蘸使得Cu凸点顶端黏附有8 ~ 12 μm厚度的Cu焊膏,接着将芯片与基板进行对中并在甲酸气氛下160 ~ 200 ℃烧结键合.

![]() 图 24 浸蘸转移法进行焊膏图形化[68]Figure 24. Process sequence of the dipping method. (a) preparation of a Cu ink film; (b) dip into Cu ink film by Cu pillar chip; (c) ink transfer and alignment to substrate; (d) joint formed by nanoparticle sintering

图 24 浸蘸转移法进行焊膏图形化[68]Figure 24. Process sequence of the dipping method. (a) preparation of a Cu ink film; (b) dip into Cu ink film by Cu pillar chip; (c) ink transfer and alignment to substrate; (d) joint formed by nanoparticle sintering研究人员首先研究了Cu凸点的轮廓形态、浸蘸转移的速度、焊膏粘度等对图形化的影响,结果表明该方法具有良好的稳定性,可以适应一定的工艺波动[71]. 并重点分析了键合压力对界面烧结组织和性能的影响,结果如图25所示. 从图中可以看到,键合压力对烧结组织的孔隙率有明显影响,无压烧结情况下烧结组织出现明显的聚集性孔洞,可靠性存在隐患,且剪切强度只有约10 MPa;随着压力增大到50 MPa,界面组织趋于致密,剪切强度提升至40 MPa左右. 该方法率先将Cu纳米焊膏应用到先进封装互连领域,并表现出良好的适用性,具有良好的应用前景,但相关可靠性测试数据还比较少,需要进一步研究. 此外,由于Cu纳米焊膏具有一定的流动性,易在压力作用下发生挤出从而导致相邻焊点“桥接”,所以该方法在实现窄节距互连上面临一定局限性.

![]() 图 25 键合压力对接头组织和剪切强度的影响[71]Figure 25. Effects of bonding pressure on microstructures and interconnect resistance. (a) microstructures; (b) interconnect resistance

图 25 键合压力对接头组织和剪切强度的影响[71]Figure 25. Effects of bonding pressure on microstructures and interconnect resistance. (a) microstructures; (b) interconnect resistance此外,Mimatsu等人[72]基于Cu纳米颗粒粉末提出了类似的转移方法进行图形化. 研究人员将通过化学法合成的Au纳米颗粒粉末铺匀到裸硅片上,再将带金凸点的芯片与裸硅片压到一起并加热到100 ℃,使得Au纳米颗粒与金凸点表面发生一定程度的预烧结,最后将芯片与基板对中键合到一起.这种方法最大的问题是纳米颗粒粉末与凸点间的结合很弱,部分凸点上没有或只有很少的纳米颗粒附着.

清华大学邹贵生团队最新提出了基于脉冲激光沉积(Pulsed Laser Deposition,PLD)技术图形化制备Cu纳米颗粒并用于Cu-Cu低温键合的方法. 如图26所示,该方法通过PLD沉积工艺制备出Cu纳米颗粒,并以光刻胶作沉积掩膜,随后剥离去除光刻胶即可获得由纳米颗粒构成的凸点阵列(直径60 μm、节距120 μm). 在250 ℃,9 MPa,10 min,甲酸气氛键合条件下,剪切强度达52.2 MPa,键合前高度约10 μm的凸点被压缩至约4 μm. 与具有流动性的纳米焊膏相比,PLD制备出的纳米颗粒为全固态结构,因此加压过程中不易出现溢出导致焊点短路的问题. 此外,该方法制备出的凸点具有良好的塑性变形能力和低温互连性能.未来可继续深入对该方法的电学性能、服役可靠性等方面的研究.

5. 结论

(1) 随着主流Sn基软钎焊工艺逐渐无法满足未来先进封装互连的要求,Cu-Cu键合技术凭借其可实现窄节距、高性能互连且与半导体制造工艺兼容性好等优势脱颖而出,成为先进封装互连的重要发展方向.

(2) 为了降低Cu-Cu键合温度,研究人员提出了通过晶粒定向生长、飞行切割、插入式互连结构等方法来提高Cu原子扩散速率以及采用等离子体轰击、金属或有机物作钝化层来减少/防止Cu表面氧化的方法.

(3) 混合键合在窄节距互连时将Cu-Cu及介质-介质分别键合起来,键合后的介质起到下填料的作用,具有更优的热/机械可靠性. 混合键合包括Cu/SiO2、Cu/粘结剂键合两类,键合时工艺要综合考虑Cu-Cu键合及介质-介质键合两方面.

(4) 热压键合和混合键合对待键合表面的粗糙度、光洁度、晶圆翘曲程度等有严格要求,往往需要昂贵、复杂的平坦化工艺及较高的键合压力来保证键合表面充分接触. 此外,混合键合技术在应用于2.5D互连时也面临一定挑战.

(5) 近年来,基于纳米材料烧结实现Cu-Cu低温键合逐步获得关注. 纳米材料具有低温连接、界面填缝等优势,可降低工艺要求. 研究人员采用定向生长纳米线、脱合金制备纳米多孔骨架、浸蘸转移纳米焊膏、PLD沉积纳米颗粒等方法分别实现了焊点图形化和Cu-Cu低温键合,并在降低键合温度、压力、适应基板翘曲等方面表现出一定潜力,但仍需要更多的性能、可靠性测试作支撑. 目前纳米材料烧结连接应用于Cu-Cu键合的研究还处于起步阶段,未来继续开发出宽工艺冗余、窄节距图形化、优良互连性能的纳米材料互连方式仍大有可为.

-

图 1 由(111) 取向的纳米孪晶Cu凸点实现Cu-Cu键合[15-17]

Figure 1. Cu-Cu bonding enabled by (111)-oriented nanotwinned Cu bumps. (a) The microbump cross-section analyzed by FIB; (b) surface orientation of an nt-Cu microbump observed by EBSD; (c) cross-sectional FIB ion-image of a Cu joint bonded at 300 ℃/93 MPa/10 s; (d) cross-sectional FIB ion-image for post-annealed sample

图 2 飞行切割[19]

Figure 2. Fly-cutting. (a) schematic illustration of fly-cutting; (b) optical images of cut Cu bumps surface

图 3 飞行切割细化表面晶粒[20]

Figure 3. Fly-cutting process introduces finer grains. (a) SEM image of initial Cu surface; (b) EBSD image of initial Cu surface; (c) SEM image of cut Cu surface; (d) EBSD image of cut Cu surface

图 4 插入式Cu-Cu键合的原理图[22]

Figure 4. Schematic of pillar-concave bonding scheme

图 5 键合后的SEM图像[22]

Figure 5. SEM cross-sectional view of Cu-Cu bonding. (a) with bonding condition of 150 ℃, 1 min, 500 MPa; (b) bottom bonding interface; (c) sidewall bonding interface

图 7 采用钝化层的Cu-Cu键合机理[30]

Figure 7. Schematic of Cu-Cu bonding with passivation layer

图 8 Ti作钝化层的键合结果[26]

Figure 8. Ti passivation bonded results. (a) SEM image; (b) TEM image

图 9 自组装分子层钝化方法的原理和工艺流程[31]

Figure 9. Schematic illustration and process flow of self-assembled monolayer method. (a) before bonding; (b) after bonding

图 10 Cu-Cu键合界面的TEM图像[32]

Figure 10. TEM micrographs of bonded Cu layers. (a) without SAM passivation; (b) with SAM passivation

图 11 等离子体活化键合的原理[40]

Figure 11. Schematic of plasma activated bonding

图 12 DBI流程示意图[41]

Figure 12. DBI technology process flow

图 13 DBI键合后的界面SEM图像[42]

Figure 13. SEM image of bonded interface by DBI method

图 14 Si作为SiO2-SiO2室温键合的中间层[44]

Figure 14. Bonding of SiO2 and SiO2 at room temperature using Si ultrathin film

图 15 基于SAB的混合键合流程示意图[46]

Figure 15. Process flow of the combined SAB with (a) UHV bonding and (b) hydrophilic bonding

图 17 Cu和粘结剂混合键合方式[50]

Figure 17. Cu/adhesive hybrid bonding. (a) “adhesive-first” hybrid bonding process; (b) “Cu-first” hybrid bonding process

图 18 制备晶圆级窄节距纳米线阵列[55]

Figure 18. Nanowiring of fine pitch pads on a wafer

图 19 键合前后的Cu纳米线[56]

Figure 19. Cu nanowires before and after bonding. (a) entire wafer covered with Cu nanowires; (b) 5 μm pads with 10 μm pitch; (c) cross sections of about 60 μm and; (d) 10 μm pitch connected with nanowires

图 20 Cu纳米多孔骨架的图形化路线[62]

Figure 20. Process flow for fabrication of patterned np-Cu foam films

图 21 纳米多孔骨架的组织形态[62]

Figure 21. Morphology of dealloyed np-Cu foam film. (a) low magnification; (b) high magnification

图 22 250 ℃/9 MPa/30 min烧结条件下的键合界面[62]

Figure 22. Cross-sectional images of the sintered joint under the condition of 250 ℃/9 MPa/30 min

图 23 不同互连技术的示意图[67]

Figure 23. Schematic of different packaging technology. (a) advanced packaging technology; (b) power device packaging technology

图 24 浸蘸转移法进行焊膏图形化[68]

Figure 24. Process sequence of the dipping method. (a) preparation of a Cu ink film; (b) dip into Cu ink film by Cu pillar chip; (c) ink transfer and alignment to substrate; (d) joint formed by nanoparticle sintering

图 25 键合压力对接头组织和剪切强度的影响[71]

Figure 25. Effects of bonding pressure on microstructures and interconnect resistance. (a) microstructures; (b) interconnect resistance

-

[1] Moore G E. Cramming more components onto integrated circuits[J]. Proceedings of the IEEE, 1998, 86(1): 82 − 85. doi: 10.1109/JPROC.1998.658762

[2] Waldrop M M. The chips are down for Moore’s law[J]. Nature News, 2016, 530(7589): 144. doi: 10.1038/530144a

[3] Li Y, Goyal D. Introduction to 3D microelectronic packaging[M]. 3D Microelectronic Packaging, Springer, 2021.

[4] Shahane N M. Reliable fine-pitch chip-to-substrate copper interconnections with high-through assembly and high power-handling[D]. Georgia Institute of Technology, 2018.

[5] Miller L F. Controlled collapse reflow chip joining[J]. IBM Journal of Research and Development, 1969, 13(3): 239 − 250. doi: 10.1147/rd.133.0239

[6] Kim J M, Shin Y E, Fujimoto K. Dynamic modeling for resin self-alignment mechanism[J]. Microelectronics Reliability, 2004, 44(6): 983 − 992. doi: 10.1016/j.microrel.2004.01.006

[7] Fang M, Tang C, Chen Y, et al. Thermo-compression bonding process characteristics and shape control of Cu-pillar microbump joints by optimizing of solder melting[J]. Journal of Materials Science: Materials in Electronics, 2022, 33(13): 10471 − 10485. doi: 10.1007/s10854-022-08034-x

[8] Zhang L, Ou S, Huang J, et al. Effect of current crowding on void propagation at the interface between intermetallic compound and solder in flip chip solder joints[J]. Applied Physics Letters, 2006, 88(1): 012106. doi: 10.1063/1.2158702

[9] Wang S, Hsu L, Wang N, et al. EBSD investigation of Cu-Sn IMC microstructural evolution in Cu/Sn-Ag/Cu microbumps during isothermal annealing[J]. Journal of Electronic Materials, 2014, 43(1): 219 − 228. doi: 10.1007/s11664-013-2675-z

[10] Chen K N, Fan A, Tan C, et al. Bonding parameters of blanket copper wafer bonding[J]. Journal of Electronic Materials, 2006, 35(2): 230 − 234. doi: 10.1007/BF02692440

[11] Chen K N, Fan A, Reif R. Microstructure examination of copper wafer bonding[J]. Journal of Electronic Materials, 2001, 30(4): 331 − 335. doi: 10.1007/s11664-001-0039-6

[12] Chen K N, Tan C S, Fan A, et al. Morphology and bond strength of copper wafer bonding[J]. Electrochemical and Solid-State Letters, 2004, 7(1): G14. doi: 10.1149/1.1626994

[13] Grayson A C R, Cima M J, Langer R. Size and temperature effects on poly (lactic-co-glycolic acid) degradation and microreservoir device performance[J]. Biomaterials, 2005, 26(14): 2137 − 2145. doi: 10.1016/j.biomaterials.2004.06.033

[14] Juang J Y, Lu C L, Chen K J, et al. Copper-to-copper direct bonding on highly (111)-oriented nanotwinned copper in no-vacuum ambient[J]. Scientific Reports, 2018, 8(1): 13910. doi: 10.1038/s41598-018-32280-x

[15] Juang J Y, Lu C L, Li Y J, et al. A solid state process to obtain high mechanical strength in Cu-to-Cu joints by surface creep on (111)-oriented nanotwins Cu[J]. Journal of Materials Research and Technology, 2021, 14: 719 − 730. doi: 10.1016/j.jmrt.2021.06.099

[16] Shie K C, Juang J Y, Chen C. Instant Cu-to-Cu direct bonding enabled by (111)-oriented nanotwinned Cu bumps[J]. Japanese Journal of Applied Physics, 2020, 59(SB): SBBA03. doi: 10.7567/1347-4065/ab5697

[17] Ong J J, Shie K C, Tu K N, et al. Two-step fabrication process for die-to-die and die-to-wafer Cu-Cu bonds[C]//2021 IEEE 71th Electronic Components and Technology Conference (ECTC), 2021: 203 − 210.

[18] Liu C M, Lin H W, Huang Y S, et al. Low-temperature direct copper-to-copper bonding enabled by creep on (111) surfaces of nanotwinned Cu[J]. Scientific Reports, 2015, 5(1): 1 − 11. doi: 10.9734/JSRR/2015/14076

[19] Sakai T, Imaizumi N, Miyajima T. Low temperature Cu-Cu direct bonding for 3D-IC by using fine crystal layer[C]//2012 2nd IEEE Transactions on Components, Packaging and Manufacturing Technology Symposium Japan, 2012: 1 − 4.

[20] Al Farisi M S, Hirano H, Tanaka S. Low-temperature hermetic thermo-compression bonding using electroplated copper sealing frame planarized by fly-cutting for wafer-level MEMS packaging[J]. Sensors and Actuators A: Physical, 2018, 279: 671 − 679. doi: 10.1016/j.sna.2018.06.021

[21] Yang Y T, Chou T C, Yu T Y, et al. Low-temperature Cu-Cu direct bonding using pillar–concave structure in advanced 3-D heterogeneous integration[J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2017, 7(9): 1560 − 1566. doi: 10.1109/TCPMT.2017.2720468

[22] Chou T C, Yang K M, Li J C, et al. Investigation of pillar–concave structure for low-temperature Cu–Cu direct bonding in 3D/2.5D heterogeneous integration[J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2020, 10(8): 1296 − 1303. doi: 10.1109/TCPMT.2020.3004969

[23] Takagi H, Kikuchi K, Maeda R, et al. Surface activated bonding of silicon wafers at room temperature[J]. Applied Physics Letters, 1996, 68(16): 2222 − 2224. doi: 10.1063/1.115865

[24] Suga T, Mu F. Surface activated bonding method for low temperature bonding[C]// 2018 7th Electronic System-Integration Technology Conference (ESTC), 2018: 1 − 4.

[25] Shigetou A, Itoh T, Sawada K, et al. Bumpless interconnect of 6-μm-pitch Cu electrodes at room temperature[J]. IEEE Transactions on Advanced Packaging, 2008, 31(3): 473 − 478. doi: 10.1109/TADVP.2008.920644

[26] Huang Y P, Chien Y S, Tzeng R N, et al. Novel Cu-to-Cu bonding with Ti passivation at 180 ℃ in 3D integration[J]. IEEE Electron Device Letters, 2013, 34(12): 1551 − 1553. doi: 10.1109/LED.2013.2285702

[27] Panigrahi A K, Bonam S, Ghosh T, et al. Ultra-thin Ti passivation mediated breakthrough in high quality Cu-Cu bonding at low temperature and pressure[J]. Materials Letters, 2016, 169: 269 − 272. doi: 10.1016/j.matlet.2016.01.126

[28] Liu D, Chen P C, Chou T C, et al. Demonstration of low-temperature fine-pitch Cu/SiO hybrid bonding by Au passivation[J]. IEEE Journal of the Electron Devices Society, 2021, 9: 868 − 875. doi: 10.1109/JEDS.2021.3114648

[29] Chou T C, Huang S Y, Chen P J, et al. Electrical and reliability investigation of Cu-to-Cu bonding with silver passivation layer in 3D integration[J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2020, 11(1): 36 − 42.

[30] Hong Z J, Liu D, Hu H W, et al. Ultra-High strength Cu-Cu bonding under low thermal budget for chiplet heterogeneous applications[C]// 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), 2021: 347 − 352.

[31] Peng L, Zhang L, Fan J, et al. Ultrafine pitch (6 μm) of recessed and bonded Cu–Cu interconnects by three-dimensional wafer stacking[J]. IEEE Electron Device Letters, 2012, 33(12): 1747 − 1749. doi: 10.1109/LED.2012.2218273

[32] Tan C S, Lim D F, Singh S G, et al. Cu–Cu diffusion bonding enhancement at low temperature by surface passivation using self-assembled monolayer of alkane-thiol[J]. Applied Physics Letters, 2009, 95(19): 192108. doi: 10.1063/1.3263154

[33] Di Cioccio L, Gueguen P, Taibi R, et al. An overview of patterned metal/dielectric surface bonding: mechanism, alignment and characterization[J]. Journal of the Electrochemical Society, 2011, 158(6): 81. doi: 10.1149/1.3577596

[34] Moriceau H, Rieutord F, Fournel F, et al. Low temperature direct bonding: An attractive technique for heterostructures build-up[J]. Microelectronics Reliability, 2012, 52(2): 331 − 41. doi: 10.1016/j.microrel.2011.08.004

[35] Liang D, Fang A W, Park H, et al. Low-temperature, strong SiO2-SiO2 covalent wafer bonding for III–V compound semiconductors-to-silicon photonic integrated circuits[J]. Journal of Electronic Materials, 2008, 37(10): 1552 − 1559. doi: 10.1007/s11664-008-0489-1

[36] Baklanov M, Shamiryan D, Tökei Z, et al. Characterization of Cu surface cleaning by hydrogen plasma[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 2001, 19(4): 1201 − 1211.

[37] Écija D, Gallego J M, Miranda R. The adsorption of atomic N and the growth of copper nitrides on Cu (1 0 0)[J]. Surface Science, 2009, 603(15): 2283 − 2289. doi: 10.1016/j.susc.2009.04.039

[38] Ito F, Shobha H, Tagami M, et al. Effective Cu surface pre-treatment for high-reliable 22 nm-node Cu dual damascene interconnects with high plasma resistant ultra low-k dielectric (k= 2.2)[J]. Microelectronic Engineering, 2012, 92: 62 − 66. doi: 10.1016/j.mee.2011.01.077

[39] Park M, Baek S, Kim S, et al. Argon plasma treatment on Cu surface for Cu bonding in 3D integration and their characteristics[J]. Applied Surface Science, 2015, 324: 168 − 173. doi: 10.1016/j.apsusc.2014.10.098

[40] 王晨曦, 王特, 许继开, 等. 晶圆直接键合及室温键合技术研究进展[J]. 精密成形工程, 2018, 10(1): 67 − 73. doi: 10.3969/j.issn.1674-6457.2018.01.008 Wang Chenxi, Wang Te, Xu Jikai, et al. Research progress of wafer direct bonding and room-temperature bonding technology[J]. Journal of Netshape Forming Engineering, 2018, 10(1): 67 − 73. doi: 10.3969/j.issn.1674-6457.2018.01.008

[41] Ko C T, Chen K N. Low temperature bonding technology for 3D integration[J]. Microelectronics Reliability, 2012, 52(2): 302 − 311. doi: 10.1016/j.microrel.2011.03.038

[42] Enquist P, Fountain G, Petteway C, et al. Low cost of ownership scalable copper direct bond interconnect 3D IC technology for three dimensional integrated circuit applications[C]//2009 IEEE International Conference on 3D System Integration, 2009: 1 − 6.

[43] Gao G, Mirkarimi L, Workman T, et al. Development of low temperature direct bond interconnect technology for die-to-wafer and die-to-die applications-stacking, yield improvement, reliability assessment[C]//2018 IEEE International Wafer Level Packaging Conference (IWLPC), 2018: 1 − 7.

[44] Utsumi J, Ide K, Ichiyanagi Y. Bonding of SiO2 and SiO2 at room temperature using Si ultrathin film[J]. ECS Transactions, 2016, 75(9): 355 − 361. doi: 10.1149/07509.0355ecst

[45] Utsumi J, Ide K, Ichiyanagi Y. Cu/SiO2 hybrid bonding obtained by surface-activated bonding method at room temperature using Si ultrathin films[J]. Micro and Nano Engineering, 2019, 2: 1 − 6. doi: 10.1016/j.mne.2018.11.004

[46] He R, Fujino M, Yamauchi A, et al. Combined surface activated bonding technique for low-temperature Cu/dielectric hybrid bonding[J]. Journal of Solid State Science and Technology, 2016, 5(7): 419. doi: 10.1149/2.0201607jss

[47] Hsiao Z C, Ko C T, Chang H H, et al. Cu/BCB hybrid bonding with TSV for 3D integration by using fly cutting technology[C]// 2015 International Conference on Electronics Packaging and iMAPS All Asia Conference (ICEP-IAAC), 2015: 834 − 837.

[48] Takeda K, Aoki M. 3D integration technology using hybrid wafer bonding and via-last TSV process[C]// 2014 IEEE International Interconnect Technology Conference, 2014: 211 − 214.

[49] Yu R, Liu F, Polastre R, et al. Reliability of a 300-mm-compatible 3DI technology based on hybrid Cu-adhesive wafer bonding[C]//2009 Symposium on VLSI Technology, 2009: 170 − 171.

[50] He R, Fujino M, Akaike M, et al. Combined surface activated bonding using H-containing HCOOH vapor treatment for Cu/Adhesive hybrid bonding at below 200 °C[J]. Applied Surface Science, 2017, 414: 163 − 170. doi: 10.1016/j.apsusc.2017.03.168

[51] He R, Suga T. Effects of Ar plasma and Ar fast atom bombardment (FAB) treatments on Cu/polymer hybrid surface for wafer bonding[C]//2014 International Conference on Electronics Packaging (ICEP), 2014: 78 − 81.

[52] Kagawa Y, Fujii N, Aoyagi K, et al. Novel stacked CMOS image sensor with advanced Cu2Cu hybrid bonding[C]//2016 IEEE International Electron Devices Meeting (IEDM), 2016: 8.4.1 − 8.4.4.

[53] Buffat P, Borel J P. Size effect on the melting temperature of gold particles[J]. Physical Review A, 1976, 13(6): 2287 − 2298. doi: 10.1103/PhysRevA.13.2287

[54] Feng B, Shen D, Wang W, et al. Cooperative bilayer of lattice-disordered nanoparticles as room-temperature sinterable nanoarchitecture for device integrations[J]. ACS Applied Materials & Interfaces, 2019, 11(18): 16972 − 16980.

[55] Roustaie F, Quednau S, Dassinger F, et al. Room temperature interconnection technology for bonding fine pitch bumps using NanoWiring, KlettWelding, KlettSintering and KlettGlueing[C]//2020 15th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), 2020: 168 − 171.

[56] Roustaie F, Quednau S, Weissenborn F, et al. Room temperature KlettWelding interconnect technology for high performance CMOS logic[C]//2021 IEEE 71st Electronic Components and Technology Conference (ECTC), 2021: 371 − 376.

[57] Strahringer D, Roustaie F, Weissenborn F, et al. Optimizing the Nano Wiring and KlettSintering parameters for low-temperature die to DCB attach of power electronic chips[C]//2021 16th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), 2021: 31 − 34.

[58] Yu Z, Tan Y Z, Bayer C F, et al. Cu-Cu Thermocompression bonding with Cu-nanowire films for power semiconductor die-attach on DBC substrates[C]//2021 IEEE 23rd Electronics Packaging Technology Conference (EPTC), 2021: 1 − 7.

[59] Shahane N, Mohan K, Behera R, et al. Novel high-temperature, high-power handling all-Cu interconnections through low-temperature sintering of nanocopper foams[C]//2016 IEEE 66th Electronic Components and Technology Conference (ECTC), 2016: 829 − 836.

[60] Sosa R A, Mohan K, Antoniou A, et al. Low-temperature all-Cu interconnections formed by pressure-less sintering of Cu-pillars with nanoporous-Cu caps[C]//2021 IEEE 71st Electronic Components and Technology Conference (ECTC), 2021: 390 − 394.

[61] Shahane N, Mohan K, Ramos G, et al. Enabling chip-to-substrate all-Cu interconnections: design of engineered bonding interfaces for improved manufacturability and low-temperature bonding[C]//2017 IEEE 67th Electronic Components and Technology Conference (ECTC), 2017: 968 − 975.

[62] Mohan K, Shahane N, Sosa R A, et al. Demonstration of patternable all-Cu compliant interconnections with enhanced manufacturability in chip-to-substrate applications[C]//2018 IEEE 68th Electronic Components and Technology Conference (ECTC), 2018: 301 − 307.

[63] Sosa R A, Mohan K, Nguyen L, et al. Cu pillar with nanocopper caps: the next interconnection node beyond traditional Cu pillar[C]//2019 IEEE 69th Electronic Components and Technology Conference (ECTC), 2019: 655 − 660.

[64] Zhang B, Damian A, Zijl J, et al. In-air sintering of copper nanoparticle paste with pressure-assistance for die attachment in high power electronics[J]. Journal of Materials Science: Materials in Electronics, 2021, 32(4): 4544 − 4555. doi: 10.1007/s10854-020-05196-4

[65] 李俊龙, 徐杨, 赵雪龙, 等. 铜颗粒低温烧结技术的研究进展[J]. 焊接学报, 2022, 43(3): 13 − 24. Li Junlong, Xuyang, Zhao Xuelong, et al. Research progress of low temperature sintering technology for Cu particles[J]. Transactions of the China Welding Institution, 2022, 43(3): 13 − 24.

[66] Guo R, Xiao Y, Gao Y, et al. Interfacial enhancement of Ag and Cu particles sintering using (111)-oriented nanotwinned Cu as substrate for die-attachment[J]. China Welding, 2022, 31(1): 22 − 28.

[67] Del Carro L. Sintering of copper nanoparticle pastes for microelectronic packaging[D]. Swiss Federal Institute of Technology in Zurich, 2018.

[68] Del Carro L, Kossatz M, Schnackenberg L, et al. Laser sintering of dip-based all-copper interconnects[C]//2018 IEEE 68th Electronic Components and Technology Conference (ECTC), 2018: 279 − 286.

[69] Del Carro L, Zürcher J, Drechsler U, et al. Low-temperature dip-based all-copper interconnects formed by pressure-assisted sintering of copper nanoparticles[J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2019, 9(8): 1613 − 1622. doi: 10.1109/TCPMT.2019.2891111

[70] Zürcher J, Yu K, Schlottig G, et al. Nanoparticle assembly and sintering towards all-copper flip chip interconnects[C]//2015 IEEE 65th Electronic Components and Technology Conference (ECTC), 2015: 1115 − 1121.

[71] Zürcher J, Del Carro L, Schlottig G, et al. All-copper flip chip interconnects by pressureless and low temperature nanoparticle sintering[C]//2016 IEEE 66th Electronic Components and Technology Conference (ECTC), 2016: 343 − 349.

[72] Mimatsu H, Mizuno J, Kasahara T, et al. Low-temperature gold-gold bonding using selective formation of nanoporous powders for bump interconnects[C]//2014 IEEE 27th International Conference on Micro Electro Mechanical Systems (MEMS), 2014: 1131 − 1134.

-

期刊类型引用(4)

1. 罗灿琳,林畅,曾煌杰,张永爱,孙捷,严群,吴朝兴,郭太良,周雄图. 电镀法制备超高密度Cu/Sn凸点和Cu/SnAg凸点及其微观形貌研究. 光电子技术. 2025(01): 10-17 .  百度学术

百度学术

2. 杜荣葆,邹贵生,王帅奇,刘磊. 金属纳米材料低温键合及图形化制备研究进展. 焊接学报. 2023(12): 82-96+142-143 .  本站查看

本站查看

3. 赵鑫宇,刘强,程国文,林铁松,黄永德. 镀铜碳纳米管对铜基复合薄膜组织及性能的影响. 焊接学报. 2023(12): 56-62+140-141 .  本站查看

本站查看

4. 王小伟,王凤江. Sn-58Bi微焊点组织与力学性能的尺寸效应行为. 焊接学报. 2023(12): 70-74+81+141-142 .  本站查看

本站查看

其他类型引用(3)

下载:

下载: